Cp3bt26 – National CP3BT26 User Manual

Page 98

www.national.com

98

CP3BT26

18.3.9

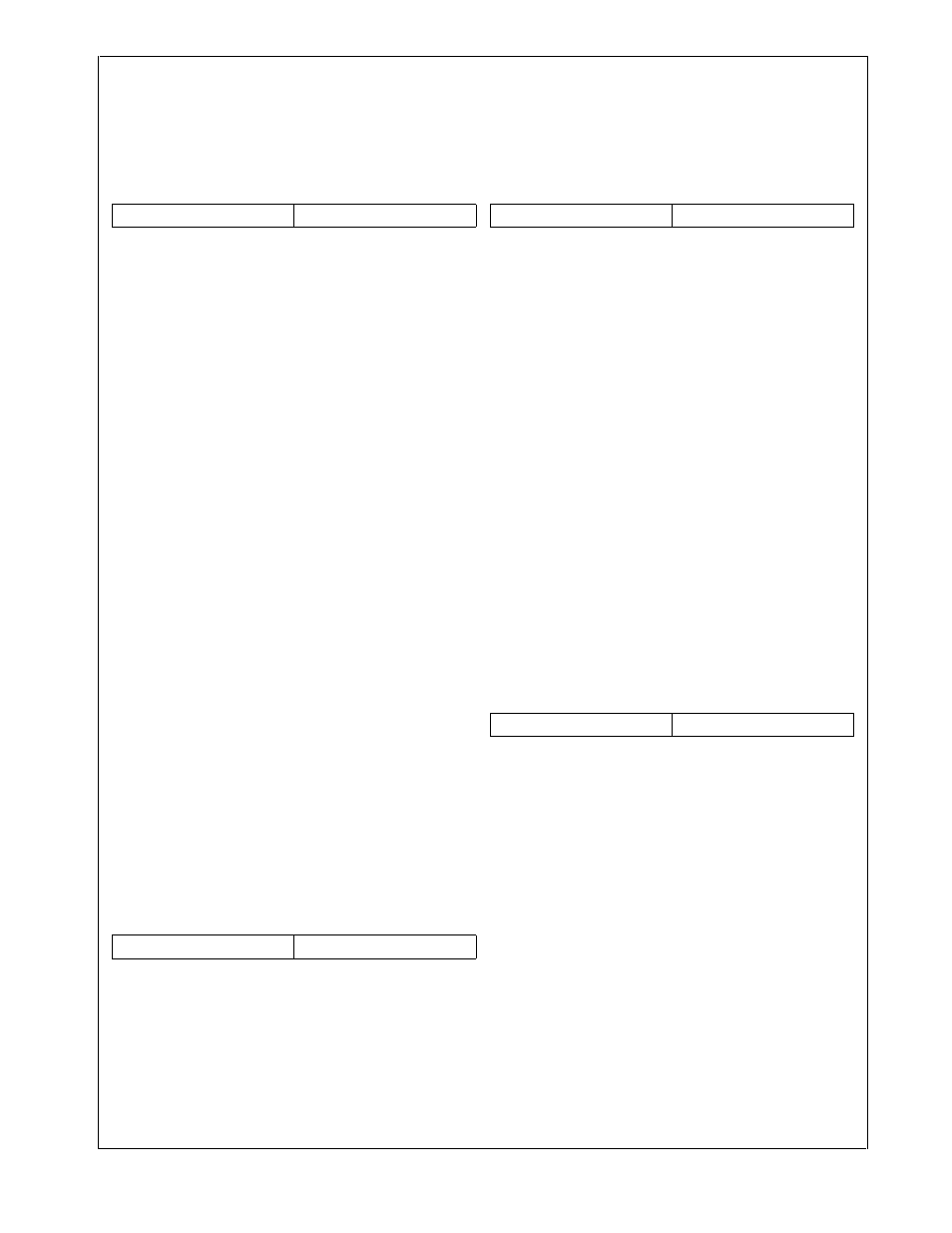

Receive Event Register (RXEV)

The RXEV register reports the current status of the FIFO,

used by the three Receive Endpoints. The RXEV register is

clear after reset. It provides read-only access from the CPU

bus.

RXFIFO

The Receive FIFO n are set whenever either

RX_ERR or RX_LAST in the respective Re-

ceive Status registers (RXSn) are set. Read-

ing the corresponding RXSn register

automatically clears these bits. The CR16

USB node discards all packets for Endpoint 0

received with errors. This is necessary in case

of retransmission due to media errors, ensur-

ing that a good copy of a SETUP packet is

captured. Otherwise, the FIFO may potentially

be tied up, holding corrupted data and unable

to receive a retransmission of the same pack-

et (the RXFIFO0 bit only reflects the value of

RX_LAST for Endpoint 0). If data streaming is

used for the receive endpoints (EP2, EP4 and

EP6), software must check the respective

RX_ERR bits to ensure the packets received

are not corrupted by errors.

RXOVRRN

The Receive Overrun n bits are set when an

overrun condition is indicated in the corre-

sponding receive FIFO n. They are cleared

when the register is read. Software must

check the respective RX_ERR bits that pack-

ets received for the other receive endpoints

(EP2, EP4 and EP6) are not corrupted by er-

rors, as these endpoints support data stream-

ing (packets which are longer than the actual

FIFO depth).

18.3.10 Receive Mask Register (RXMSK)

The RXMSK register is used to select the bits of the RXEV

register, which cause the RX_EV bit in the MAEV register to

be set. When set and the corresponding bit in the RXEV

register is set, RX_EV bit in the MAEV register is set. When

clear, the corresponding bit in the RXEV register does not

cause the RX_EV bit to be set. The RXMSK register pro-

vides read/write access. This register is clear after reset.

18.3.11 NAK Event Register (NAKEV)

A bit in the NAKEV register is set when a Negative Acknowl-

edge (NAK) was generated by the corresponding endpoint.

The NAKEV register provides read-only access from the

CPU bus. It is clear after reset.

IN

The IN n bits are set when a NAK handshake

is generated for an enabled address/endpoint

combination (AD_EN in the Function Ad-

dress, FAR, register is set and EP_EN in the

Endpoint Control, EPCx, register is set) in re-

sponse to an IN token. These bits are cleared

when the register is read.

OUT

The OUT n bits are set when a NAK hand-

shake is generated for an enabled address/

endpoint combination (AD_EN in the FAR reg-

ister is set and EP_EN in the EPCx register is

set) in response to an OUT token. These bits

are not set if NAK is generated as result of an

overrun condition. They are cleared when the

register is read.

18.3.12 NAK Mask Register (NAKMSK)

The NAKMSK register is used to select the bits of the NA-

KEV register, which cause the NAK bit in the MAEV register

to be set. When set and the corresponding bit in the NAKEV

register is set, the NAK bit in the MAEV register is set. When

cleared, the corresponding bit in the NAKEV register does

not cause NAK to be set. The NAKMSK register provides

read/write access. It is clear after reset.

7

4

3

0

RXOVRRN

RXFIFO

7

4

3

0

RXOVRRN

RXFIFO

7

4

3

0

OUT

IN

7

4

3

0

OUT

IN