11 microwire/spi timing, Microwire/spi timing, Cp3 bt26 – National CP3BT26 User Manual

Page 253

253

www.national.com

CP3

BT26

30.11

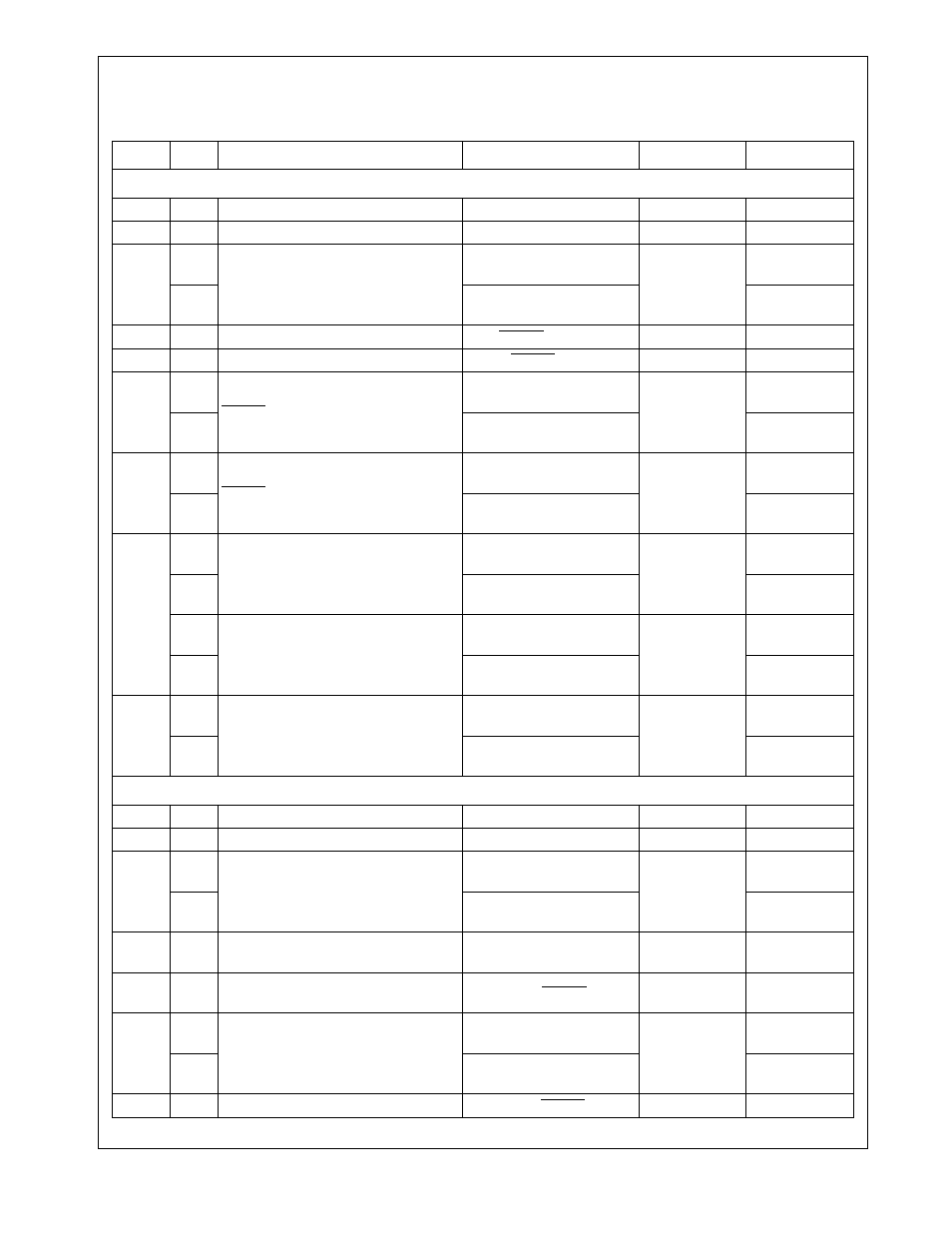

MICROWIRE/SPI TIMING

Table 88

Microwire/SPI Signals

Symbol Figure

Description

Reference

Min (ns)

Max (ns)

Microwire/SPI Input Signals

t

MSKh

Microwire Clock High

At 2.0V (both edges)

80

-

t

MSKl

Microwire Clock Low

At 0.8V (both edges)

80

-

t

MSKp

Microwire Clock Period

SCIDL bit = 0; Rising Edge

(RE) MSK to next RE MSK

200

-

SCIDL bit = 1; Falling Edge

(FE) MSK to next FE MSK

-

t

MSKh

MSK Hold (slave only)

After MWCS goes inactive

40

-

t

MSKs

MSK Setup (slave only)

Before MWCS goes active

80

-

t

MWCSh

MWCS Hold (slave only)

SCIDL bit = 0: After FE

MSK

40

-

SCIDL bit = 1: After RE

MSK

-

t

MWCSs

MWCS Setup (slave only)

SCIDL bit = 0: Before RE

MSK

80

-

SCIDL bit = 1: Before FE

MSK

-

t

MDIh

Microwire Data In Hold (master)

Normal Mode: After RE

MSK

0

-

Alternate Mode: After FE

MSK

-

Microwire Data In Hold (slave)

Normal Mode: After RE

MSK

40

-

Alternate Mode: After FE

MSK

-

t

MDIs

Microwire Data In Setup

Normal Mode: Before RE

MSK

80

-

Alternate Mode: Before FE

MSK

-

Microwire/SPI Output Signals

t

MSKh

Microwire Clock High

At 2.0V (both edges)

40

-

t

MSKl

Microwire Clock Low

At 0.8V (both edges)

40

-

t

MSKp

Microwire Clock Period

SCIDL bit = 0: Rising Edge

(RE) MSK to next RE MSK

100

-

SCIDL bit = 1: Falling Edge

(FE) MSK to next FE MSK

-

t

MSKd

MSK Leading Edge Delayed (master

only)

Data Out Bit #7 Valid

0.5 t

MSK

1.5 t

MSK

t

MDOf

Microwire Data Float

b

(slave only)

After RE on MWCS

-

25

t

MDOh

Microwire Data Out Hold

Normal Mode: After FE

MSK

0.0

-

Alternate Mode: After RE

MSK

t

MDOnf

Microwire Data No Float

(slave only)

After FE on MWCS

0

25