Cp3 bt26 – National CP3BT26 User Manual

Page 87

87

www.national.com

CP3

BT26

16.5.6

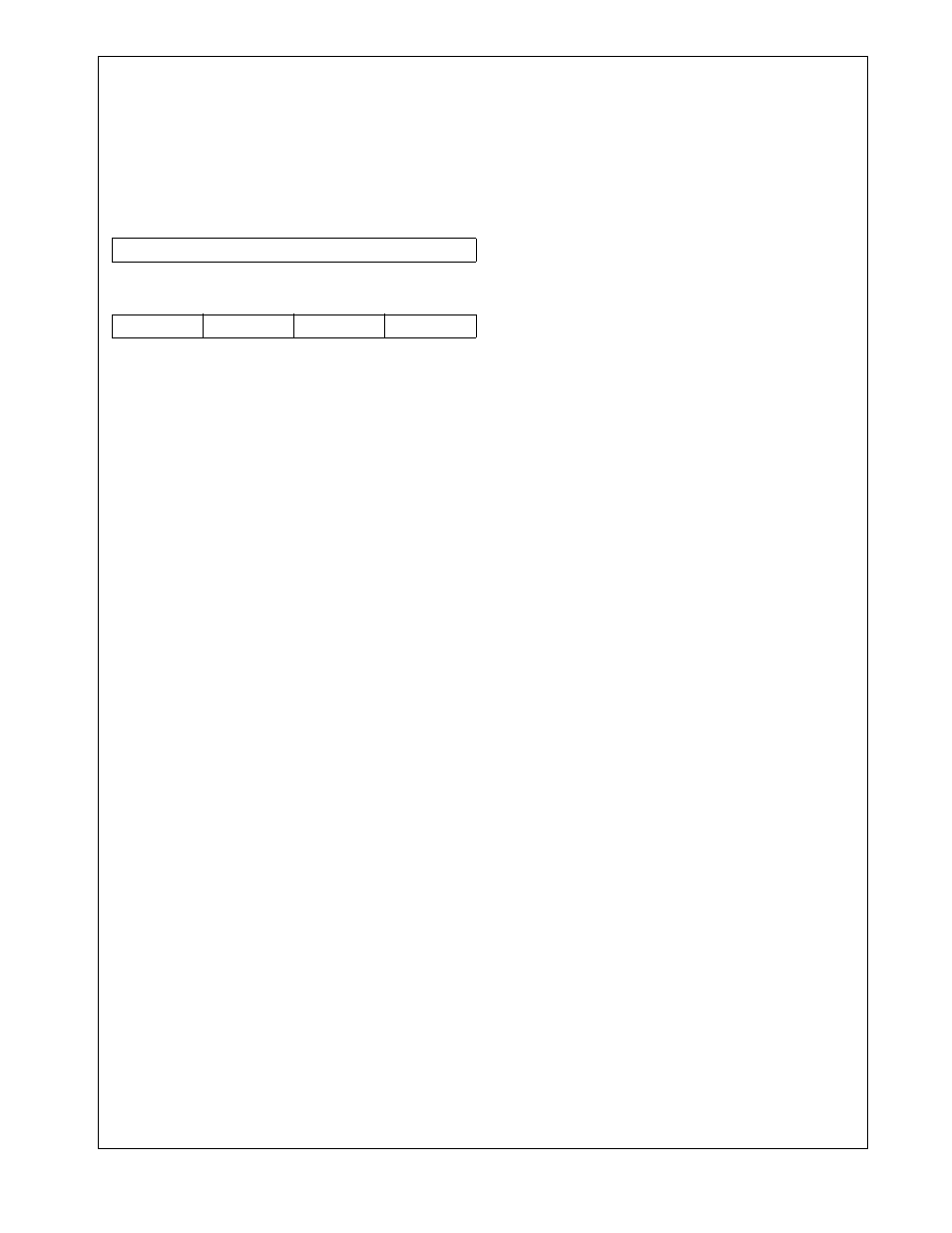

ADC Result Register (ADCRESLT)

The ADCRESLT register includes the software-visible end

of a 4-word FIFO. Conversion results are loaded into the

FIFO from the 12-bit ADC and unloaded when software

reads the ADCRESLT register. The ADCRESLT register is

read-only. With the exception of the PEN_DOWN bit, the

fields in this register are cleared when the register is read.

ADC_RESULT The ADC Result field holds a 12-bit value for

the conversion result. If the ADC_DONE bit is

clear, there is no valid result in this field, and

the field will have a value of 0. The

ADC_RESULT field and the SIGN bit together

form the software-visible end of the ADC

FIFO.

SIGN

The Sign bit indicates whether the - input has

a voltage greater than the + input (differential

mode only). For example if AD-

CGCR.MUX_CFG is 000b, ADC0 is the + in-

put and ADC1 is the - input. If the voltage on

ADC0 is greater than the voltage on ADC1,

the SIGN bit will be 0; if the voltage on ADC0

is less than the voltage on ADC1, the SIGN bit

will be 1. In single-ended mode, this bit always

reads as 0.

0 – In differential mode, + input has a voltage

greater than the - input. In single-ended

mode, this bit is always 0.

1 – In differential mode, - input has a voltage

greater than the + input.

PEN_DOWN The Pen-Down bit indicates whether a pen-

down condition is being sensed. To enable

pen-down detection, the TOUCH_CFG field of

the ADCGCR register must be loaded with

101b. When pen-down detection is enabled

and a pen-down condition is sensed, the

PEN_DOWN bit is set. This bit is not carried

through the FIFO, so its value represents the

current status of the pen-down detector.

When pen-down detection is enabled, the sig-

nal from the pen-down detector is ORed with

the Done signal to generate the wake-up sig-

nal (WUI30) passed to the MIWU unit. If pen-

down detection is not enabled, this bit reads

as 0.

0 – No pen-down condition is sensed, or pen-

down detection is disabled.

1 – Pen-down condition is sensed.

ADC_OFLW The ADC FIFO Overflow bit indicates whether

the 4-word FIFO behind the ADCRESLT reg-

ister has overflowed. When this occurs, the

most recent conversion result is lost. This bit

is cleared when the ADCRESLT register is

read.

0 – FIFO overflow has not occurred.

1 – FIFO overflow has occurred.

ADC_DONE The ADC Done bit indicates when an ADC

conversion has completed. When this bit is

set, the data in the ADC_RESULT field is val-

id. When this bit is clear, there is no valid data

in the ADC_RESULT field. The Done bit is

cleared when the ADCRESLT register is read,

but if there are queued conversion results in

the FIFO, the Done bit will become set again

after one System Clock period.

0 – No ADC conversion has completed since

the ADCRESLT register was last read.

1 – An ADC conversion has completed since

the ADCRESLT register was last read.

11

0

ADC_RESULT

15

14

13

12

ADC_DONE

ADC_OFLW PEN_DOWN

SIGN