Cp3bt26 – National CP3BT26 User Manual

Page 138

www.national.com

138

CP3BT26

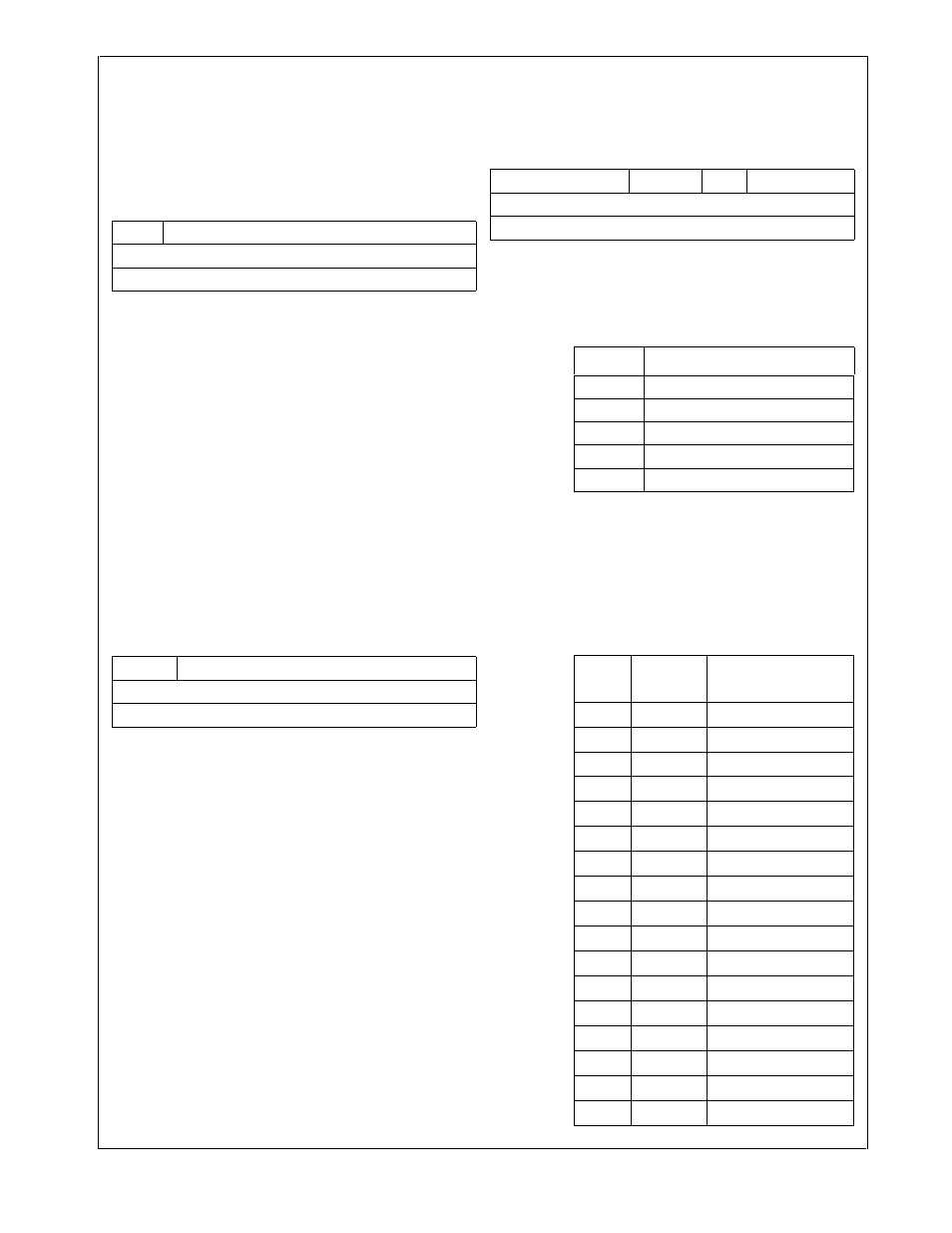

19.10.12 CAN Interrupt Clear Register (CICLR)

The CICLR register bits individually clear CAN interrupt

pending flags caused by the message buffers and from the

Error Management Logic. Do not modify this register with in-

structions that access the register as a read-modify-write

operand, such as the bit manipulation instructions.

EICLR

The Error Interrupt Clear bit is used to clear

the EIPND bit.

0 – The EIPND bit is unaffected by writing 0.

1 – The EIPND bit is cleared by writing 1.

ICLR

The Buffer Interrupt Clear bits are used to

clear the IPND bits.

0 – The corresponding IPND bit is unaffected

by writing 0.

0 – The corresponding IPND bit is cleared by

writing 1.

19.10.13 CAN Interrupt Code Enable Register (CICEN)

The CICEN register controls whether the interrupt pending

flag in the CIPND register is translated into the Interrupt

Code field of the CSTPND register. All interrupt requests,

CAN error, and message buffer interrupts can be enabled/

disabled separately for the interrupt code indication field.

EICEN

The Error Interrupt Code Enable bit controls

encoding for error interrupts.

0 – Error interrupt pending is not indicated in

the interrupt code.

1 – Error interrupt pending is indicated in the

interrupt code.

ICEN

The Buffer Interrupt Code Enable bits control

encoding for message buffer interrupts.

0 – Message buffer interrupt pending is not

indicated in the interrupt code.

1 – Message buffer interrupt pending is indi-

cated in the interrupt code.

19.10.14 CAN Status Pending Register (CSTPND)

The CSTPND register holds the status of the CAN Node

and the Interrupt Code.

NS

The CAN Node Status field indicates the sta-

tus of the CAN node as shown in Table 61.

IRQ/IST

The IRQ bit and IST field indicate the interrupt

source of the highest priority interrupt current-

ly pending and enabled in the CICEN register.

Table 62 shows the several interrupt codes

when the encoding for all interrupt sources is

enabled (CICEN = FFFFh).

15

14

0

EICLR

ICLR

0

W

15

14

0

EICEN

ICEN

0

R/W

15

8

7

5

4

3

0

Reserved

NS

IRQ

IST

0

R

Table 61

CAN Node Status

NS

Node Status

000

Not Active

010

Error Active

011

Error Warning Level

10X

Error Passive

11X

Bus Off

Table 62

Highest Priority Interrupt Code

IRQ

IST3:0

CAN Interrupt

Request

0

0000

No interrupt request

1

0000

Error interrupt

1

0001

Buffer 0

1

0010

Buffer 1

1

0011

Buffer 2

1

0100

Buffer 3

1

0101

Buffer 4

1

0110

Buffer 5

1

0111

Buffer 6

1

1000

Buffer 7

1

1001

Buffer 8

1

1010

Buffer 9

1

1011

Buffer 10

1

1100

Buffer 11

1

1101

Buffer 12

1

1110

Buffer 13

1

1111

Buffer 14