Cp3 bt26 – National CP3BT26 User Manual

Page 157

157

www.national.com

CP3

BT26

20.7.9

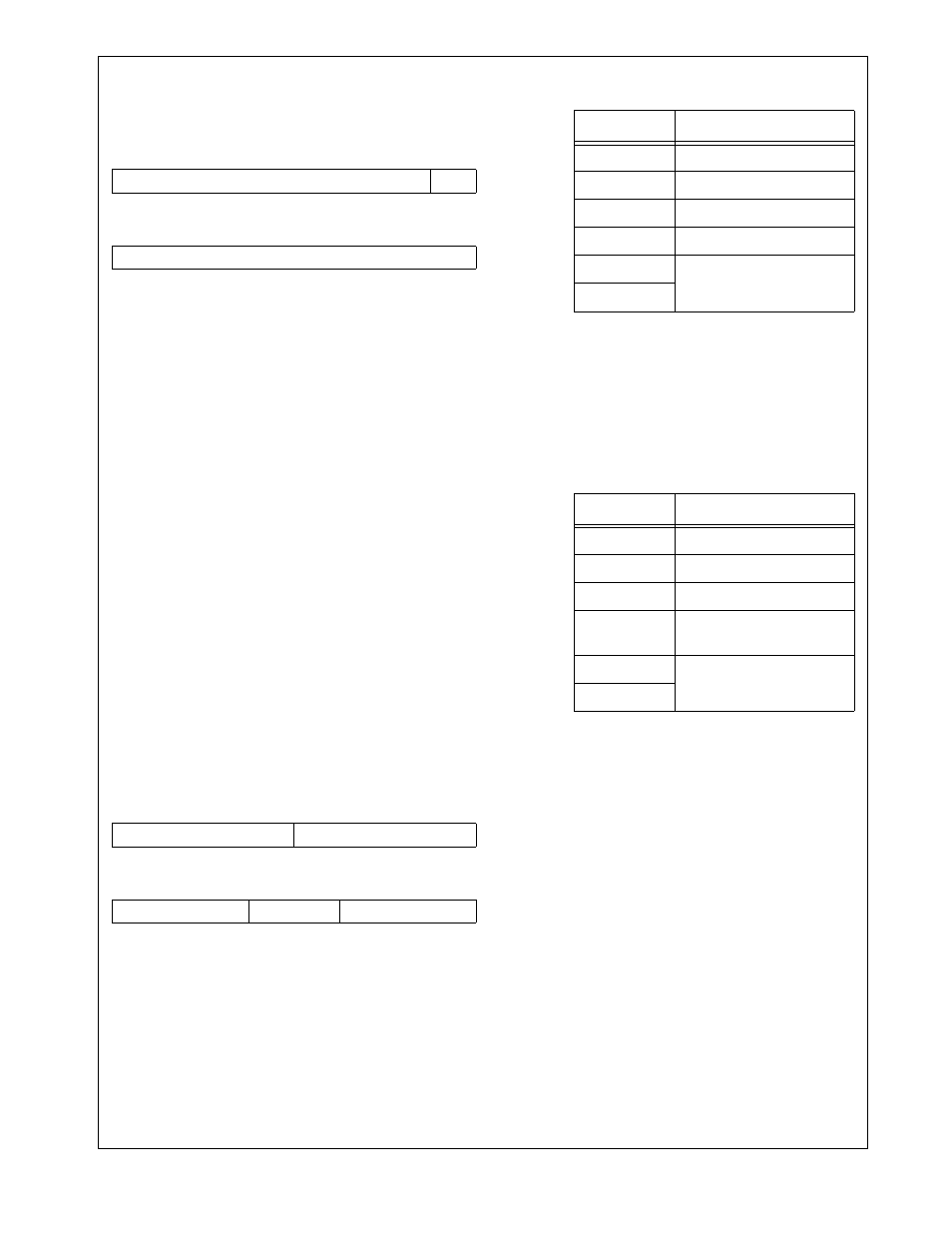

Audio Clock Control Register (ACCR)

The ACCR register is used to control the bit timing of the au-

dio interface. After reset, this register is clear.

CSS

The Clock Source Select bit selects one out of

two possible clock sources for the audio inter-

face. After reset, the CSS bit is clear.

0 – The Auxiliary Clock 1 is used to clock the

Audio Interface.

1 – The 48-MHz USB clock is used to clock

the Audio Interface.

FCPRS

The Frame Clock Prescaler is used to divide

the bit clock to generate the frame clock for

the receive and transmit operations. The bit

clock is divided by (FCPRS + 1). After reset,

the FCPRS field is clear. The maximum al-

lowed bit clock rate to achieve an 8 kHz frame

clock is 1024 kHz. This value must be set cor-

rectly even if the frame sync is generated ex-

ternally.

BCPRS

The Bit Clock Prescaler is used to divide the

audio interface clock (selected by the CSS bit)

to generate the bit clock for the receive and

transmit operations. The audio interface input

clock is divided by (BCPRS + 1). After reset,

the BCPRS[7:0] bits are clear.

20.7.10 Audio DMA Control Register (ADMACR)

The ADMACR register is used to control the DMA support

of the audio interface. In addition, it is used to configure the

automatic transmission of the audio control bits. After reset,

this register is clear.

RMD

The Receive Master DMA field specify which

slots (audio channels) are supported by DMA,

i.e. when a DMA request is asserted to the

DMA controller. If the RMDn bit is set for an

assigned slot n (RXDSAn = 1), a DMA request

n is asserted, when the ARDRn is full. If the

RXDSAn bit for a slot is clear, the RMDn bit is

ignored. The following table shows the receive

DMA request scheme.

TMD

The Transmit Master DMA field specifies

which slots (audio channels) are supported by

DMA, i.e. when a DMA request is asserted to

the DMA controller. If the TMD bit is set for an

assigned slot n (TXDSAn = 1), a DMA request

n is asserted, when the ATDRn register is

empty. If the TXDSA bit for a slot is clear, the

TMD bit is ignored. The following table shows

the transmit DMA request scheme.

ACD

The Audio Control Data field is used to fill the

remaining bits of a 16-bit slot if only 13, 14, or

15 bits of PCM audio data are transmitted.

ACO

The Audio Control Output field controls the

number of control bits appended to the PCM

data word.

00 – No Audio Control bits are appended.

01 – Append ACD0.

10 – Append ACD1:0.

11 – Append ACD2:0.

7

1

0

FCPRS

CSS

15

8

BCPRS

7

4

3

0

TMD

RMD

15

13

12

11

10

8

Reserved

ACO

ACD

RMD

DMA Request Condition

0000

None

0001

ARDR0 full

0010

ARDR1 full

0011

ARDR0 full or ARDR1 full

x1xx

Not supported on

CP3BT26

1xxx

TMD

DMA Request Condition

0000

None

0001

ATDR0 empty

0010

ATDR1 empty

0011

ATDR0 empty or

ATDR1 empty

x1xx

Not supported on

CP3BT26

1xxx