0 versatile timer unit (vtu), 1 vtu functional description, Versatile timer unit (vtu) – National CP3BT26 User Manual

Page 206: Vtu functional description, Cp3bt26

www.national.com

206

CP3BT26

27.0 Versatile Timer Unit (VTU)

The Versatile Timer Unit (VTU) contains four fully indepen-

dent 16-bit timer subsystems. Each timer subsystem can

operate either as dual 8-bit PWM timers, as a single 16-bit

PWM timer, or as a 16-bit counter with 2 input capture chan-

nels. These timer subsystems offers an 8-bit clock prescaler

to accommodate a wide range of system frequencies.

The VTU offers the following features:

The VTU can be configured to provide:

— Eight fully independent 8-bit PWM channels

— Four fully independent 16-bit PWM channels

— Eight 16-bit input capture channels

The VTU consists of four timer subsystems, each of

which contains:

— A 16-bit counter

— Two 16-bit capture / compare registers

— An 8-bit fully programmable clock prescaler

Each of the four timer subsystems can operate in the fol-

lowing modes:

— Low power mode, i.e. all clocks are stopped

— Dual 8-bit PWM mode

— 16-bit PWM mode

— Dual 16-bit input capture mode

The VTU controls a total of eight I/O pins, each of which

can function as either:

— PWM output with programmable output polarity

— Capture input with programmable event detection and

timer reset

A flexible interrupt scheme with

— Four separate system level interrupt requests

— A total of 16 interrupt sources each with a separate in-

terrupt pending bit and interrupt enable bit

27.1

VTU FUNCTIONAL DESCRIPTION

The VTU is comprised of four timer subsystems. Each timer

subsystem contains an 8-bit clock prescaler, a 16-bit up-

counter, and two 16-bit registers. Each timer subsystem

controls two I/O pins which either function as PWM outputs

or capture inputs depending on the mode of operation.

There are four system-level interrupt requests, one for each

timer subsystem. Each system-level interrupt request is

controlled by four interrupt pending bits with associated en-

able/disable bits. All four timer subsystems are fully inde-

pendent, and each may operate as a dual 8-bit PWM timer,

a 16-bit PWM timer, or as a dual 16-bit capture timer.

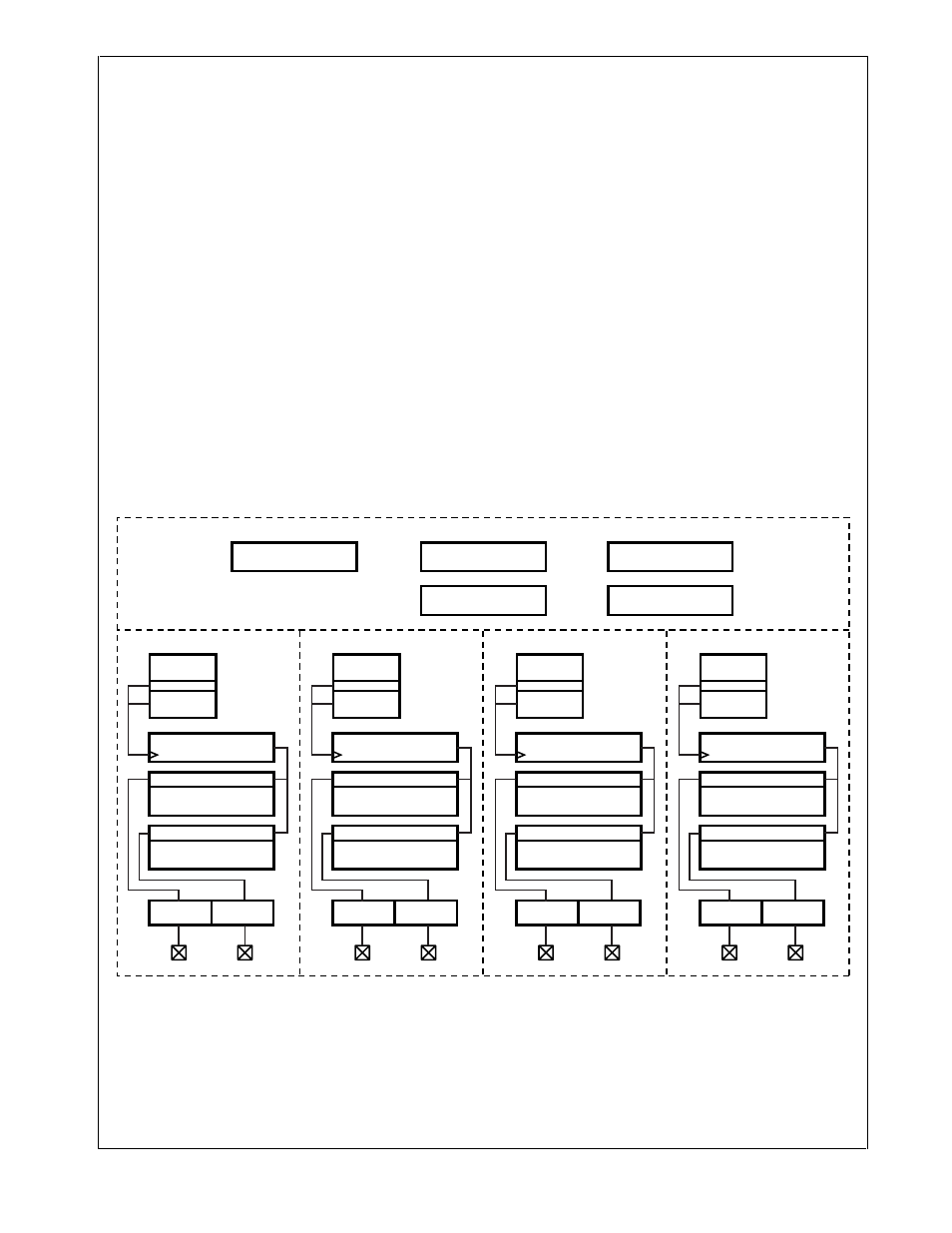

Figure 104 shows the main elements of the VTU.

Figure 104.

Versatile Timer Unit Block Diagram

INTCTL

0

15

MODE

0

15

Count1

TIO1

0

15

PERCAP1

Compare

-

Capture

DTYCAP1

Compare

-

Capture

C1 PRSC

Timer Subsystem 1

= =

7

Prescaler

Counter

I/O Control

INTPND

0

15

IO1CTL

0

15

IO2CTL

0

15

TIO2

I/O Control

Count2

TIO3

0

15

PERCAP2

Compare

-

Capture

DTYCAP2

Compare

-

Capture

C2 PRSC

= =

7

Prescaler

Counter

I/O Control

TIO4

I/O Control

Count4

TIO7

0

15

PERCAP4

Compare

-

Capture

DTYCAP4

Compare

-

Capture

C4RSC

= =

7

Prescaler

Counter

I/O Control

TIO8

I/O Control

Count3

TIO5

0

15

PERCAP3

Compare

-

Capture

DTYCAP3

Compare

-

Capture

C3 PRSC

= =

7

Prescaler

Counter

I/O Control

TIO6

I/O Control

Timer Subsystem 2

Timer Subsystem 3

Timer Subsystem 4

DS088