2 endpoint operation, Endpoint operation, Cp3 bt26 – National CP3BT26 User Manual

Page 91

91

www.national.com

CP3

BT26

18.2

ENDPOINT OPERATION

18.2.1

Address Detection

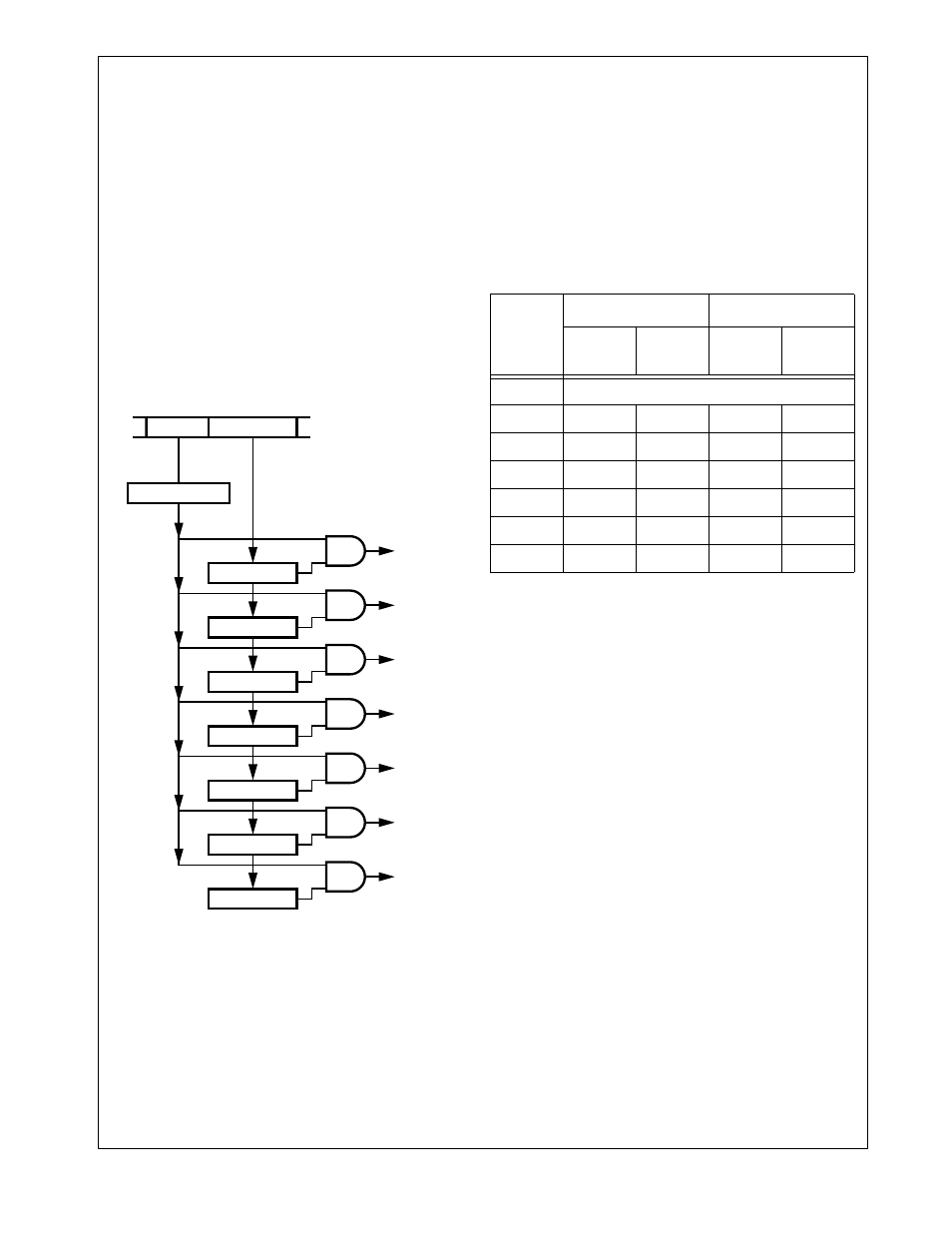

Packets are broadcast from the host controller to all nodes

on the USB network. Address detection is implemented in

hardware to allow selective reception of packets and to per-

mit optimal use of CPU bandwidth. One function address

with seven different endpoint combinations is decoded in

parallel. If a match is found, then that particular packet is re-

ceived into the FIFO; otherwise it is ignored.

The incoming USB Packet Address field and Endpoint field

are extracted from the incoming bit stream. Then the ad-

dress field is compared to the Function Address register

(FADR). If a match is detected, the Endpoint field is com-

pared to all of the Endpoint Control registers (EPCn) in par-

allel. A match then causes the payload data to be received

or transmitted using the respective endpoint FIFO.

Figure 29.

USB Function Address/Endpoint Decoding

18.2.2

Transmit and Receive Endpoint FIFOs

The CR16 USB node uses a total of seven transmit and re-

ceive FIFOs: one bidirectional transmit and receive FIFO for

the mandatory control endpoint, three transmit FIFOs, and

three receive FIFOs. As shown in Table 39, the bidirectional

FIFO for the control endpoint is 8 bytes deep. The additional

unidirectional FIFOs are 64 bytes each for both transmit and

receive. Each FIFO can be programmed for one exclusive

USB endpoint, used together with one globally decoded

USB function address. Software must not enable both trans-

mit and receive FIFOs for endpoint zero at any given time.

Table 39

Endpoint FIFO Sizes

If two endpoints in the same direction are programmed with

the same endpoint number and both are enabled, data is re-

ceived or transmitted to/from the endpoint with the lower

number, until that endpoint is disabled for bulk or interrupt

transfers, or becomes full or empty for ISO transfers. For ex-

ample, if receive EP2 and receive EP4 both use endpoint 5

and are both isochronous, the first OUT packet is received

into EP2 and the second OUT packet into EP4, assuming

no software interaction in between. For ISO endpoints, this

allows implementing a ping-pong buffer scheme together

with the frame number match logic.

Endpoints in different directions programmed with the same

endpoint number operate independently.

Receive/

Transmit FIFO0

USB Packet

EPC0 Register

FADR Register

ADDR Field

Endpoint Field

Match

Match

Transmit FIFO1

EPC1 Register

Receive FIFO1

EPC2 Register

Transmit FIFO2

EPC3 Register

Receive FIFO2

EPC4Register

Transmit FIFO3

EPC5 Register

Receive FIFO3

EPC6 Register

DS049

Endpoint

Number

TX FIFO

RX FIFO

Size

(Bytes)

Name

Size

(Bytes)

Name

0

FIFO0 (bidirectional, 8 bytes)

1

64

TXFIFO1

-

-

2

-

-

64

RXFIFO1

3

64

TXFIFO2

-

-

4

-

-

64

RXFIFO2

5

64

TXFIFO3

-

-

6

-

-

64

RXFIFO3