Cp3bt26 – National CP3BT26 User Manual

Page 194

www.national.com

194

CP3BT26

25.4.1

Timer and Watchdog Configuration Register

(TWCFG)

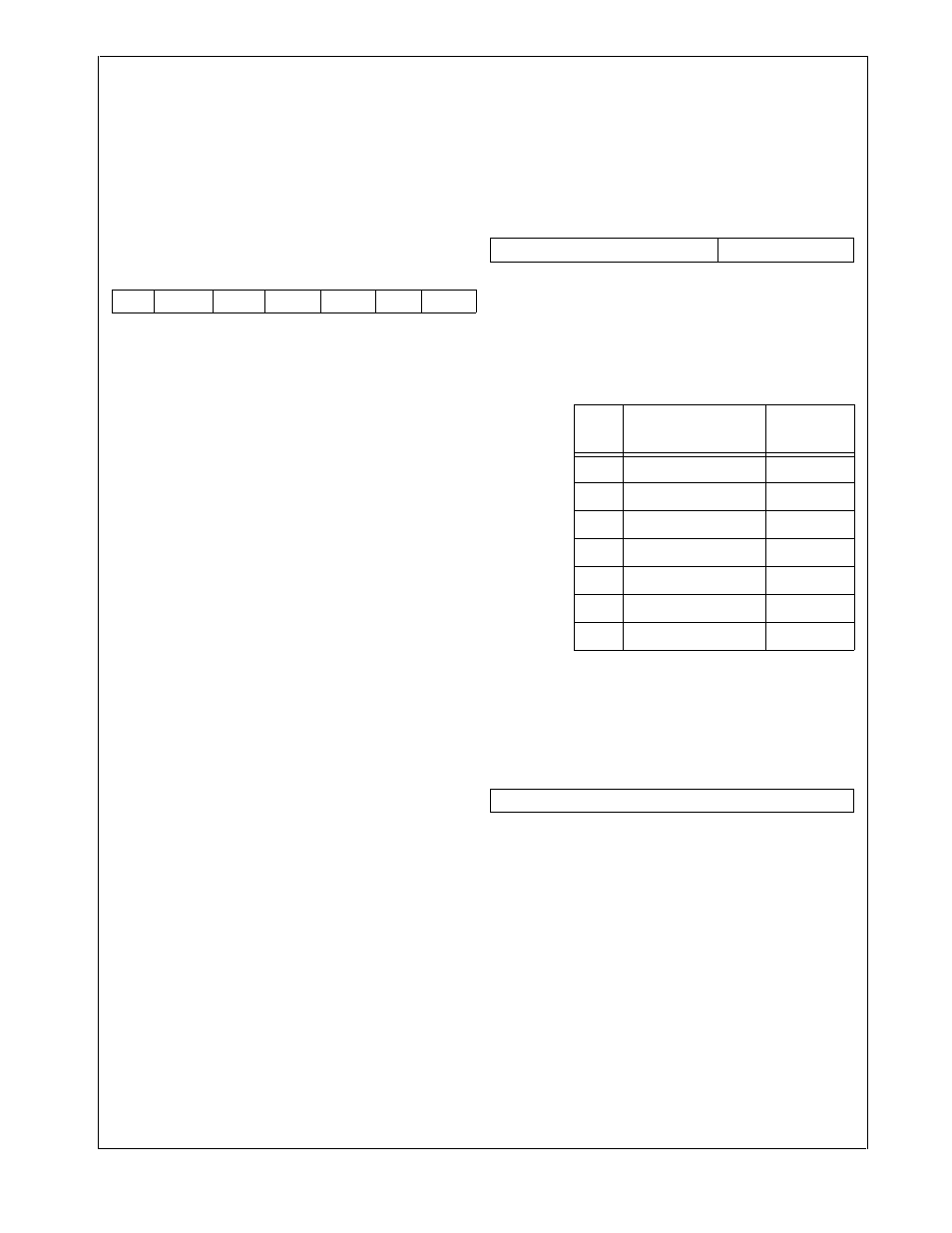

The TWCFG register is a byte-wide, read/write register that

selects the Watchdog clock input and service method, and

also allows the Watchdog registers to be selectively locked.

A locked register cannot be read or written; a read operation

returns unpredictable values and a write operation is ig-

nored. Once a lock bit is set, that bit cannot be cleared until

the device is reset. At reset, the non-reserved bits of the

register are cleared. The register format is shown below.

LTWCFG

The Lock TWCFG Register bit controls ac-

cess to the TWCFG register. When clear, ac-

cess to the TWCFG register is allowed. When

set, the TWCFG register is locked.

0 – TWCFG register unlocked.

1 – TWCFG register locked.

LTWCP

The Lock TWCP Register bit controls access

to the TWCP register. When clear, access to

the TWCP register is allowed. When set, the

TWCP register is locked.

0 – TWCP register unlocked.

1 – TWCP register locked.

LTWMT0

The Lock TWMT0 Register bit controls access

to the TWMT0 register. When clear, access to

the TWMT0 and T0CSR registers are al-

lowed. When set, the TWMT0 and T0CSR

registers are locked.

0 – TWMT0 register unlocked.

1 – TWMT0 register locked.

LWDCNT

The Lock LDWCNT Register bit controls ac-

cess to the LDWCNT register. When clear, ac-

cess to the LDWCNT register is allowed.

When set, the LDWCNT register is locked.

0 – LDWCNT register unlocked.

1 – LDWCNT register locked.

WDCT0I

The Watchdog Clock from T0IN bit selects the

clock source for the Watchdog timer. When

clear, the T0OUT signal (the output of Timer

T0) is used as the Watchdog clock. When set,

the T0IN signal (the prescaled Slow Clock) is

used as the Watchdog clock.

0 – Watchdog timer is clocked by T0OUT.

1 – Watchdog timer is clocked by T0IN.

WDSDME

The Watchdog Service Data Match Enable bit

controls which method is used to service the

Watchdog timer. When clear, Watchdog ser-

vicing is accomplished by writing a count val-

ue to the WDCNT register; write operations to

the Watchdog Service Data Match (WDSDM)

register are ignored. When set, Watchdog

servicing is accomplished by writing the value

5Ch to the WDSDM register.

0 – Write a count value to the WDCNT regis-

ter to service the Watchdog timer.

1 – Write 5Ch to the WDSDM register to ser-

vice the Watchdog timer.

25.4.2

Timer and Watchdog Clock Prescaler Register

(TWCP)

The TWCP register is a byte-wide, read/write register that

specifies the prescaler value used for dividing the low-fre-

quency clock to generate the T0IN clock. At reset, the non-

reserved bits of the register are cleared. The register format

is shown below.

MDIV

Main Clock Divide. This 3-bit field defines the

prescaler factor used for dividing the low

speed device clock to create the T0IN clock.

The allowed 3-bit values and the correspond-

ing clock divisors and clock rates are listed be-

low.

25.4.3

TWM Timer 0 Register (TWMT0)

The TWMT0 register is a word-wide, read/write register that

defines the T0OUT interrupt rate. At reset, TWMT0 register

is initialized to FFFFh. The register format is shown below.

PRESET

The Timer T0 Preset field holds the value

used to reload Timer T0 on each underflow.

Therefore, the frequency of the Timer T0 in-

terrupt is the frequency of T0IN divided by

(PRESET+1). The allowed values of PRESET

are 0001h through FFFFh.

7

6

5

4

3

2

1

0

Res. WDSDME WDCT0I LWDCNT LTWMT0 LTWCP LTWCFG

7

3

2

0

Reserved

MDIV

MDIV

Clock Divisor

(f

SCLK

= 32.768 kHz)

T0IN

Frequency

000

1

32.768 kHz

001

2

16.384 kHz

010

4

8.192 kHz

011

8

4.096 kHz

100

16

2.056 kHz

101

32

1.024 kHz

Other

Reserved

N/A

15

0

PRESET