Cp3 bt26 – National CP3BT26 User Manual

Page 55

55

www.national.com

CP3

BT26

FCLK bit cannot be cleared until the PLL clock

has stabilized. After reset this bit is set.

0

–

PLL is active.

1

–

PLL is powered down.

ACE1

When the Auxiliary Clock Enable bit is set and

a stable Main Clock is provided, the Auxiliary

Clock 1 prescaler is enabled and generates

the first Auxiliary Clock. When the ACE1 bit is

clear or the Main Clock is not stable, Auxiliary

Clock 1 is stopped. Auxiliary Clock 1 is used

as the clock input for the Bluetooth LLC and

the Advanced Audio Interface. After reset this

bit is clear.

0

–

Auxiliary Clock 1 is stopped.

1

–

Auxiliary Clock 1 is active if the Main

Clock is stable.

ACE2

When the Auxiliary Clock Enable 2 bit is set

and a stable Main Clock is provided, the Aux-

iliary Clock 2 prescaler is enabled and gener-

ates Auxiliary Clock 2. When the ACE2 bit is

clear or the Main Clock is not stable, the Aux-

iliary Clock 2 is stopped. Auxiliary Clock 2 is

used as the clock input for the CVSD/PCM

transcoder and the A/D converter. After reset

this bit is clear.

0

–

Auxiliary Clock 2 is stopped.

1

–

Auxiliary Clock 2 is active if the Main

Clock is stable.

POR

Power-On-Reset - The Power-On-Reset bit is

set when a power-turn-on condition has been

detected. This bit can only be cleared by soft-

ware, not set. Writing a 1 to this bit will be ig-

nored, and the previous value of the bit will be

unchanged.

0

–

Software cleared this bit.

1

–

Software has not cleared his bit since the

last reset.

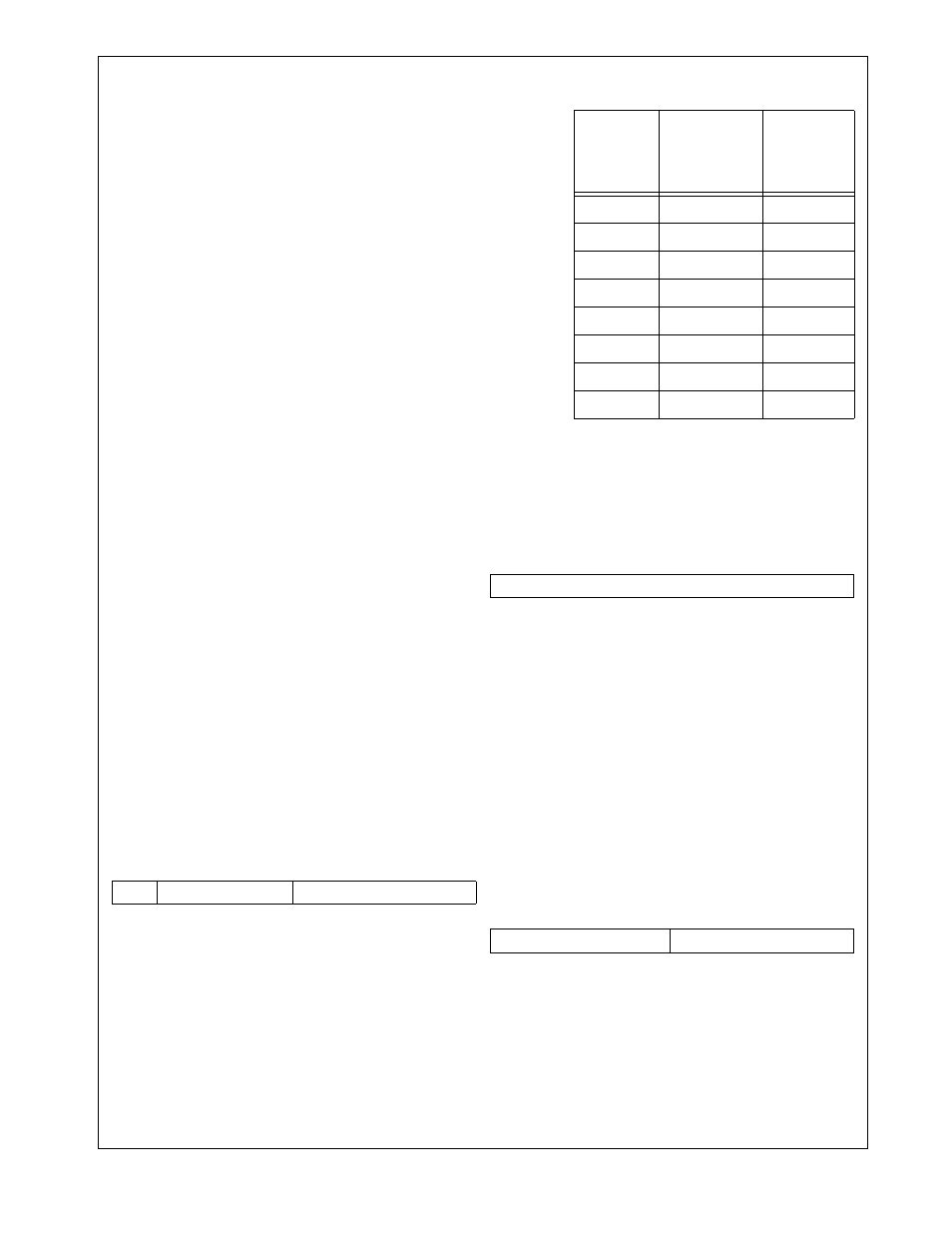

11.9.2

High Frequency Clock Prescaler Register

(PRSFC)

The PRSFC register is a byte-wide read/write register that

holds the 4-bit clock divisor used to generate the high-fre-

quency clock. In addition, the upper three bits are used to

control the operation of the PLL. The register is initialized to

4Fh at reset (except in PROG mode

.)

FCDIV

The Fast Clock Divisor specifies the divisor

used to obtain the high-frequency System

Clock from the PLL or Main Clock. The divisor

is (FCDIV + 1).

MODE

The PLL MODE field specifies the operation

mode of the on-chip PLL. After reset the

MODE bits are initialized to 100b, so the PLL

is configured to generate a 48-MHz clock.

This register must not be modified when the

System Clock is derived from the PLL Clock.

The System Clock must be derived from the

low-frequency oscillator clock while the

MODE field is modified.

11.9.3

Low Frequency Clock Prescaler Register

(PRSSC)

The PRSSC register is a byte-wide read/write register that

holds the clock divisor used to generate the Slow Clock from

the Main Clock. The register is initialized to B6h at reset.

SCDIV

The Slow Clock Divisor field specifies a divi-

sor to be used when generating the Slow

Clock from the Main Clock. The Main Clock is

divided by a value of (2 × (SCDIV + 1)) to ob-

tain the Slow Clock. At reset, the SCDIV reg-

ister is initialized to B6h, which generates a

Slow Clock rate of 32786.89 Hz. This is about

0.5% faster than a Slow Clock generated from

an external 32768 Hz crystal network.

11.9.4

Auxiliary Clock Prescaler Register (PRSAC)

The PRSAC register is a byte-wide read/write register that

holds the clock divisor values for prescalers used to gener-

ate the two auxiliary clocks from the Main Clock. The regis-

ter is initialized to FFh at reset.

ACDIV1

The Auxiliary Clock Divisor 1 field specifies

the divisor to be used for generating Auxiliary

Clock 1 from the Main Clock. The Main Clock

is divided by a value of (ACDIV1 + 1).

ACDIV2

The Auxiliary Clock Divisor 2 field specifies

the divisor to be used for generating Auxiliary

Clock 2 from the Main Clock. The Main Clock

is divided by a value of (ACDIV2 + 1).

7

6

4

3

0

Res

MODE

FCDIV

MODE2:0

Output

Frequency

(from 12 MHz

input clock)

Description

000

Reserved

Reserved

001

Reserved

Reserved

010

Reserved

Reserved

011

36 MHz

3× Mode

100

48 MHz

4× Mode

101

60 MHz

5× Mode

110

Reserved

Reserved

111

Reserved

Reserved

7

0

SCDIV

7

4

3

0

ACDIV2

ACDIV2