4 software dma request, 5 debug mode, 6 dma controller register set – National CP3BT26 User Manual

Page 43: Software dma request, Debug mode, Dma controller register set, Cp3 bt26

43

www.national.com

CP3

BT26

If the DMASTAT.VLD bit is clear:

1. The transfer operation terminates.

2. The channel sets the DMASTAT.OVR bit.

3. The DMASTAT.CHAC bit is cleared.

4. An interrupt is generated if enabled by the

DMACNTLn.EOVR bit.

The DMACNTLn.CHEN bit must be cleared before loading

the DMACNTLn register to avoid prematurely starting a new

DMA transfer.

Note: The ADCBn and ADRBn registers are used only in

indirect (memory-to-memory) transfer. In direct (flyby)

mode, the DMAC does not use them and therefore does not

copy ADRBn into ADCBn.

9.3.3

Auto-Initialize Operation

This mode allows the DMAC to continuously fill the same

memory area without software intervention.

Initialization

1. Write the block addresses and byte count into the AD-

CAn, ADCBn, and BLTCn counters, as well as the

ADRAn, ADRBn, and BLTRn registers.

2. Set the DMACNTLn.OT bit to select auto-initialize

mode.

3. Set the DMACNTLn.CHEN bit to activate the channel

and enable it to respond to DMA transfer requests.

Continuation

When the BLTCn counter reaches 0:

1. The contents of the ADRAn, ADRBn, and BLTRn regis-

ters are copied to the ADCAn, ADCBn, and BLTCn

counters.

2. The DMAC channel checks the value of the DMAS-

TAT.TC bit.

If the DMASTAT.TC bit is set:

1. The DMASTAT.OVR bit is set.

2. A level interrupt is generated if enabled by the

DMACNTLn.EOVR bit.

3. The operation is repeated.

If the DMASTAT.TC bit is clear:

1. The DMASTAT.TC bit is set.

2. A level interrupt is generated if enabled by the

DMACNTLn.ETC bit.

3. The DMAC operation is repeated.

Termination

The DMA transfer is terminated when the

DMACNTLn.CHEN bit is cleared.

9.4

SOFTWARE DMA REQUEST

In addition to the hardware requests from I/O devices, a

DMA transfer request can also be initiated by software. A

software DMA transfer request must be used for block copy-

ing between memory devices.

When the DMACNTLn.SWRQ bit is set, the corresponding

DMA channel receives a DMA transfer request. When the

DMACNTLn.SWRQ bit is clear, the software DMA transfer

request of the corresponding channel is inactive.

For each channel, use the software DMA transfer request

only when the corresponding hardware DMA request is in-

active and no terminal count interrupt is pending. Software

can poll the DMASTAT.CHAC bit to determine whether the

DMA channel is already active. After verifying the DMAS-

TATn.CHAC bit is clear (channel inactive), check the DMAS-

TATn.TC (terminal count) bit. If the TC bit is clear, then no

terminal count condition exists and therefore no terminal

count interrupt is pending. If the channel is not active and no

terminal count interrupt is pending, software may request a

DMA transfer.

9.5

DEBUG MODE

When the FREEZE signal is active, all DMA operations are

stopped. They will start again when the FREEZE signal

goes inactive. This allows breakpoints to be used in debug

systems.

9.6

DMA CONTROLLER REGISTER SET

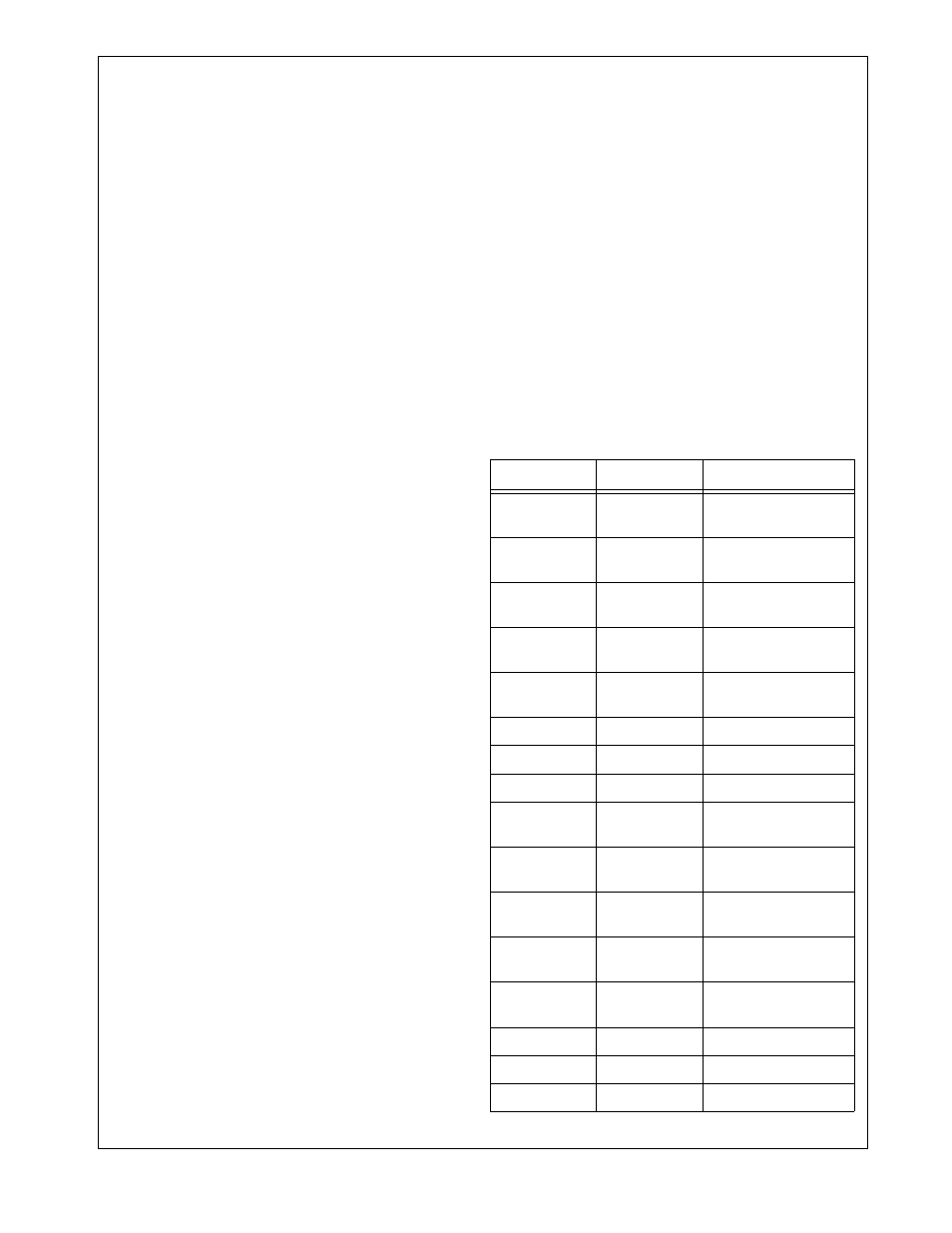

There are four identical sets of DMA controller registers, as

listed in Table 18.

Table 18

DMA Controller Registers

Name

Address

Description

ADCA0

FF F800h

Device A Address

Counter Register

ADRA0

FF F804h

Device A Address

Register

ADCB0

FF F808h

Device B Address

Counter Register

ADRB0

FF F80Ch

Device B Address

Register

BLTC0

FF F810h

Block Length

Counter Register

BLTR0

FF F814h

Block Length Register

DMACNTL0

FF F81Ch

DMA Control Register

DMASTAT0

FF F81Eh

DMA Status Register

ADCA1

FF F820h

Device A Address

Counter Register

ADRA1

FF F824h

Device A Address

Register

ADCB1

FF F828h

Device B Address

Counter Register

ADRB1

FF F82Ch

Device B Address

Register

BLTC1

FF F830h

Block Length

Counter Register

BLTR1

FF F834h

Block Length Register

DMACNTL1

FF F83Ch

DMA Control Register

DMASTAT1

FF F83Eh

DMA Status Register