Cp3bt26 – National CP3BT26 User Manual

Page 46

www.national.com

46

CP3BT26

9.6.8

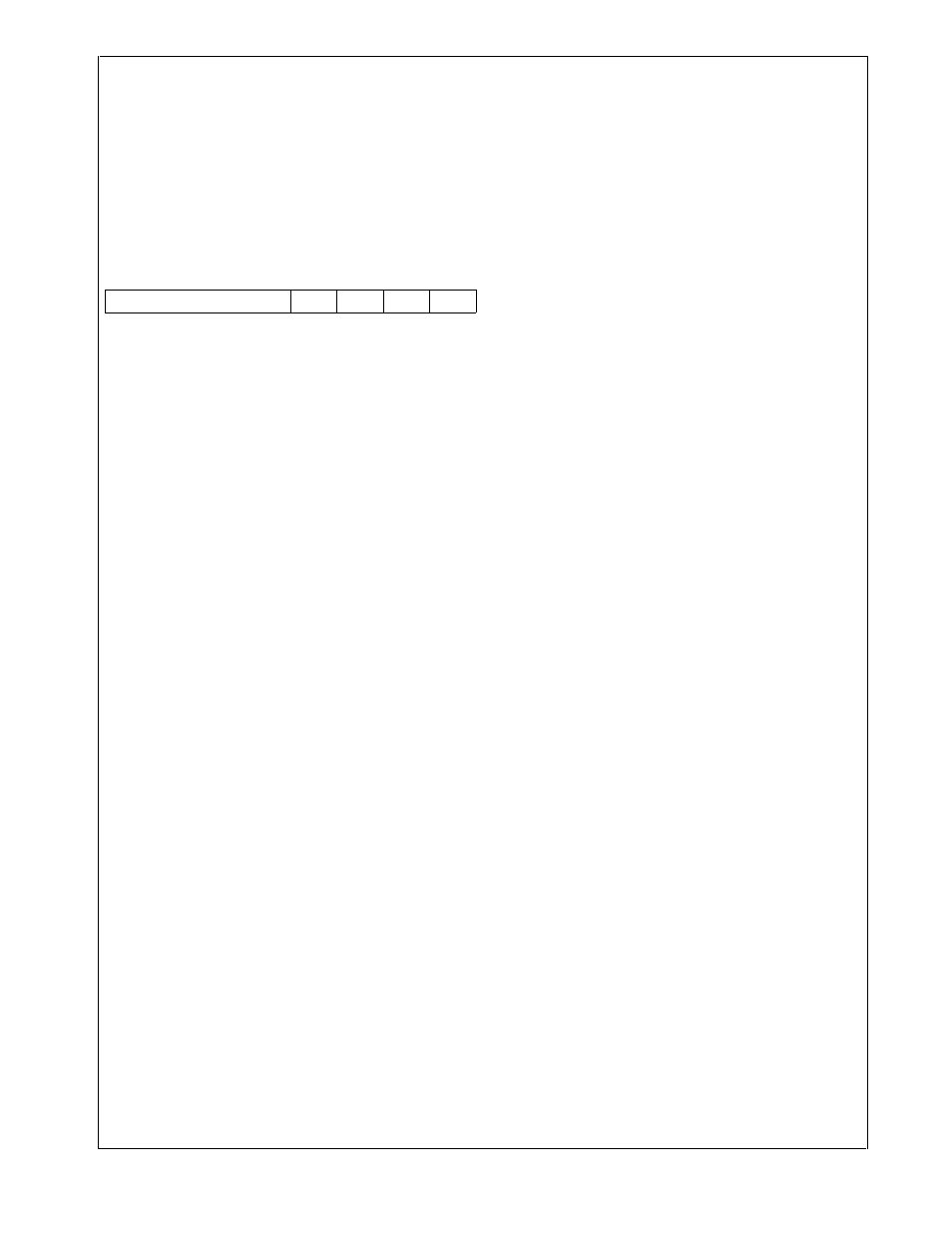

DMA Status Register (DMASTAT)

The DMA status register is a byte-wide, read register that

holds the status information for the DMA channel n. This

register is cleared at reset. The reserved bits always return

zero when read. The VLD, OVR and TC bits are sticky (once

set by the occurrence of the specific condition, they remain

set until explicitly cleared by software). These bits can be in-

dividually cleared by writing 1 to the bit positions in the DM-

ASTAT register to be cleared. Writing 0 to these bits has no

effect

TC

The Terminal Count bit indicates whether the

transfer was completed by a terminal count

condition (BLTCn Register reached 0).

0

–

Terminal count condition did not occur.

1

–

Terminal count condition occurred.

OVR

The behavior of the Channel Overrun bit de-

pends on the operation mode (single buffer,

double buffer, or auto-initialize) of the DMA

channel.

In double-buffered mode (DMACNTLn.OT =

0):

The OVR bit is set when the present transfer

is completed (BLTCn = 0), but the parameters

for the next transfer (address and block

length) are not valid (DMASTAT.VLD = 0).

In auto-initialize mode (DMACNTLn.OT = 1):

The OVR bit is set when the present transfer

is completed (BLTCn = 0), and the DMAS-

TAT.TC bit is still set.

In single-buffer mode:

Operates in the same way as double-buffer

mode. In single-buffered mode, the DMAS-

TAT.VLD bit should always be clear, so it will

also be set when the DMASTAT.TC bit is set.

Therefore, the OVR bit can be ignored in this

mode.

CHAC

The Channel Active bit continuously indicates

the active or inactive status of the channel,

and therefore, it is read only. Data written to

the CHAC bit is ignored.

0

–

Channel inactive.

1

–

Indicates that the channel is active

(CHEN bit in the CNTLn register is 1 and

BLTCn > 0)

VLD

The Transfer Parameters Valid bit specifies

whether the transfer parameters for the next

block to be transferred are valid. Writing the

BLTRn register automatically sets this bit. The

bit is cleared in the following cases:

The present transfer is completed and the

ADRAn, ADRBn (indirect mode only), and

BLTR registers are copied to the ADCAn,

ADCBn (indirect mode only), and BLTCn

registers.

Writing 1 to the VLD bit.

7

4

3

2

1

0

Reserved

VLD

CHAC OVR

TC