Cp3bt26 – National CP3BT26 User Manual

Page 244

www.national.com

244

CP3BT26

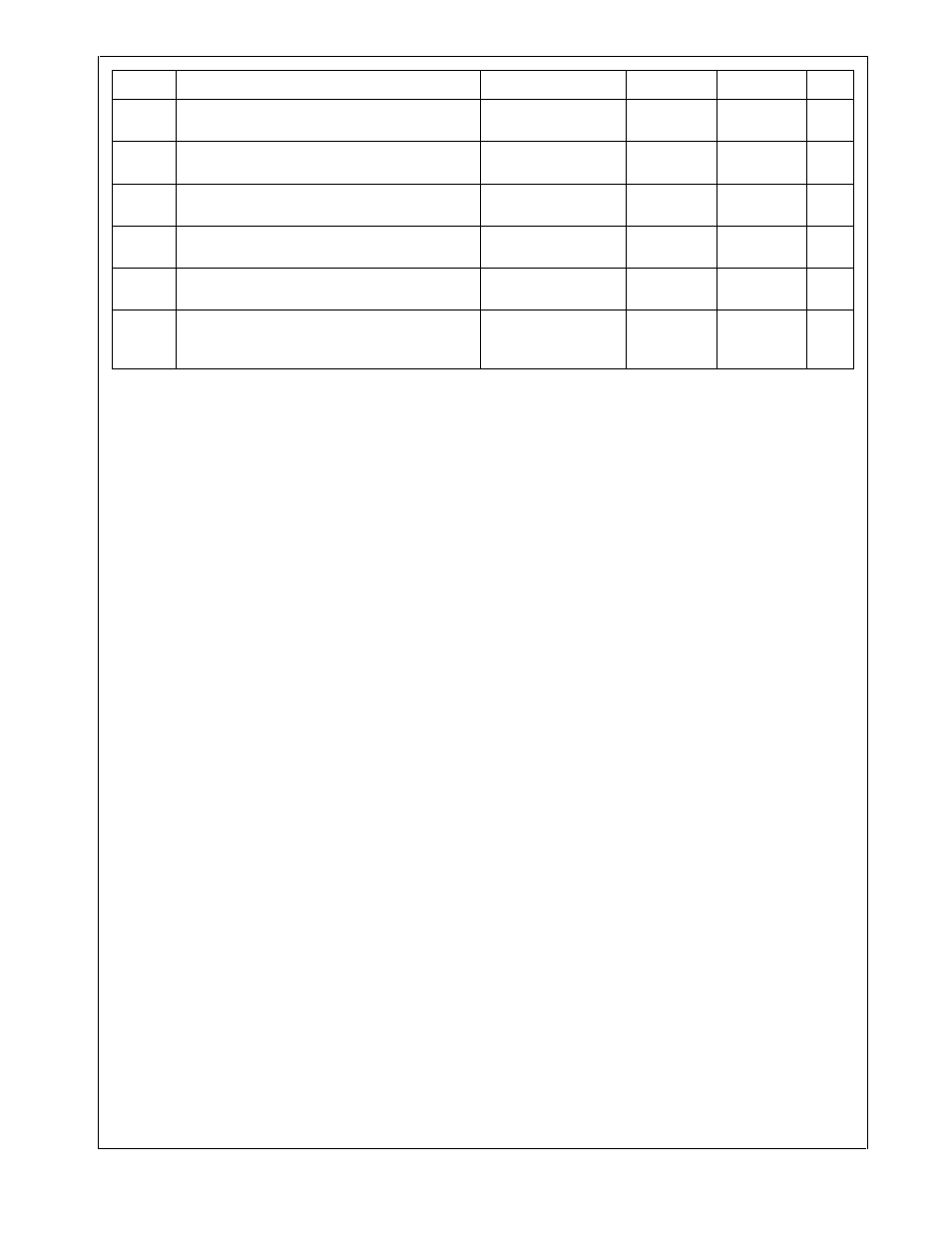

I

O(Off)

Output Leakage Current

(I/O pins in input mode)

0V

≤ Vout ≤ Vcc

-2.0

2.0

µA

Icca1

Digital Supply Current Active Mode

b

Vcc = 2.75V,

IOVcc=3.63V

20

mA

Iccprog

Digital Supply Current Active Mode

c

Vcc = 2.75V,

IOVcc = 3.63V

20

mA

Iccps

Digital Supply Current Power Save Mode

d

Vcc = 2.75V,

IOVcc =3.63V

4

mA

Iccid

Digital Supply Current Idle Mode

e

Vcc = 2.75V,

IOVcc = 3.63V

2

mA

Iccq

Digital Supply Current Halt Mode

e,f

Vcc = 2.75V,

IOVcc = 3.63V,

20°C

150

µA

a. Guaranteed by design

b. Run from internal memory (RAM), Iout = 0 mA, X1CKI = 12 MHz, PLL enabled (4×), internal system clock is

24 MHz, not programming Flash memory

c. Same conditions as Icca1, but programming or erasing Flash memory page

d. Running from internal memory (RAM), Iout = 0 mA, XCKI1 = 12 MHz, PLL disabled, X2CKI = 32.768 kHz,

device put in power-save mode, Slow Clock derived from XCKI1

e. Iout = 0 mA, XCKI1 = Vcc, X2CKI = 32.768 kHz

f. Halt current approximately doubles for every 20°C.

Symbol

Parameter

Conditions

Min

Max

Units