8 time stamp counter, Time stamp counter, Cp3bt26 – National CP3BT26 User Manual

Page 126

www.national.com

126

CP3BT26

19.7.1

Highest Priority Interrupt Code

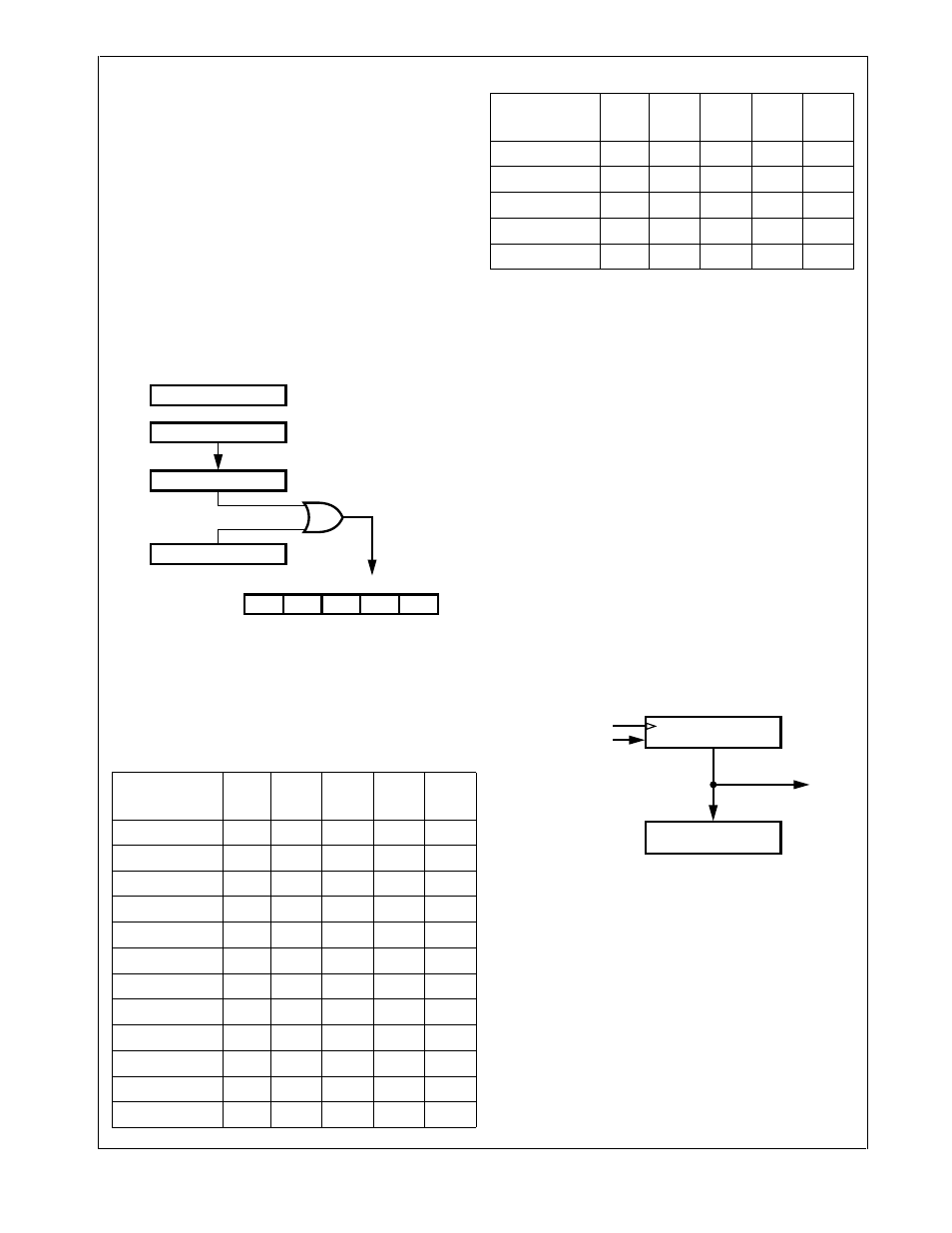

To reduce the decoding time for the CIPND register, the

buffer interrupt request with the highest priority is placed as

interrupt status code into the IST[3:0] section of the CSTP-

ND register.

Each of the buffer interrupts as well as the error interrupt

can be individually enabled or disabled in the CAN Interrupt

Enable register (CIEN). As soon as an interrupt condition

occurs, every interrupt request is indicated by a flag in the

CAN Interrupt Pending register (CIPND). When the interrupt

code logic for the present highest priority interrupt request

is enabled, this interrupt will be translated into the IST3:0

bits of the CAN Status Pending register (CSTPND). An in-

terrupt request can be cleared by setting the corresponding

bit in the CAN Interrupt Clear register (CICLR).

Figure 59 shows the CAN interrupt management.

Figure 59.

Interrupt Management

The highest priority interrupt source is translated into the

bits IRQ and IST3:0 as shown in Table 49.

19.7.2

Usage Hints

The interrupt code IST3:0 can be used within the interrupt

handler as a displacement to jump to the relevant subrou-

tine.

The CAN Interrupt Code Enable (CICEN) register is used in

the CAN interrupt handler if software is servicing all receive

buffer interrupts first, followed by all transmit buffer inter-

rupts. In this case, software can first enable only receive

buffer interrupts to be coded, then scan and service all

pending interrupt requests in the order of their priority. After

processing all the receive interrupts, software changes the

CICEN register to disable all receive buffers and enable all

transmit buffers, then services all pending transmit buffer in-

terrupt requests according to their priorities.

19.8

TIME STAMP COUNTER

The CAN module features a free running 16-bit timer (CT-

MR) incrementing every bit time recognized on the CAN

bus. The value of this timer during the ACK slot is captured

into the TSTP register of a message buffer after a success-

ful transmission or reception of a message. Figure 60

shows a simplified block diagram of the Time Stamp

counter.

Figure 60.

Time Stamp Counter

The timer can be synchronized over the CAN network by re-

ceiving or transmitting a message to or from buffer 0. In this

case, the TSTP register of buffer 0 captures the current

CTMR value during the ACK slot of a message (as above),

and then the CTMR is reset to 0000b. Synchronization can

be enabled or disabled using the CGCR.TSTPEN bit.

Table 49

Highest Priority Interrupt Code (ICEN=FFFF)

CAN Interrupt

Request

IRQ

IST3

IST2

IST1

IST0

No Request

0

0

0

0

0

Error Interrupt

1

0

0

0

0

Buffer 0

1

0

0

0

1

Buffer 1

1

0

0

1

0

Buffer 2

1

0

0

1

1

Buffer 3

1

0

1

0

0

Buffer 4

1

0

1

0

1

Buffer 5

1

0

1

1

0

Buffer 6

1

0

1

1

1

Buffer 7

1

1

0

0

0

Buffer 8

1

1

0

0

1

Buffer 9

1

1

0

1

0

CICLR

CIPND

Clear interrupt flags of every

message buffer individually

ICODE

CIEN

CICEN

IRQ

IST3

IST2

IST1

IST0

DS043

Buffer 10

1

1

0

1

1

Buffer 11

1

1

1

0

0

Buffer 12

1

1

1

0

1

Buffer 13

1

1

1

1

0

Buffer 14

1

1

1

1

1

Table 49

Highest Priority Interrupt Code (ICEN=FFFF)

CAN Interrupt

Request

IRQ

IST3

IST2

IST1

IST0

16-Bit counter

+

1

Reset

TSTP register

ACK slot

ACK slot and buffer 0 active

CAN bits on the bus

DS044