Cp3 bt26 – National CP3BT26 User Manual

Page 169

169

www.national.com

CP3

BT26

22.3.1

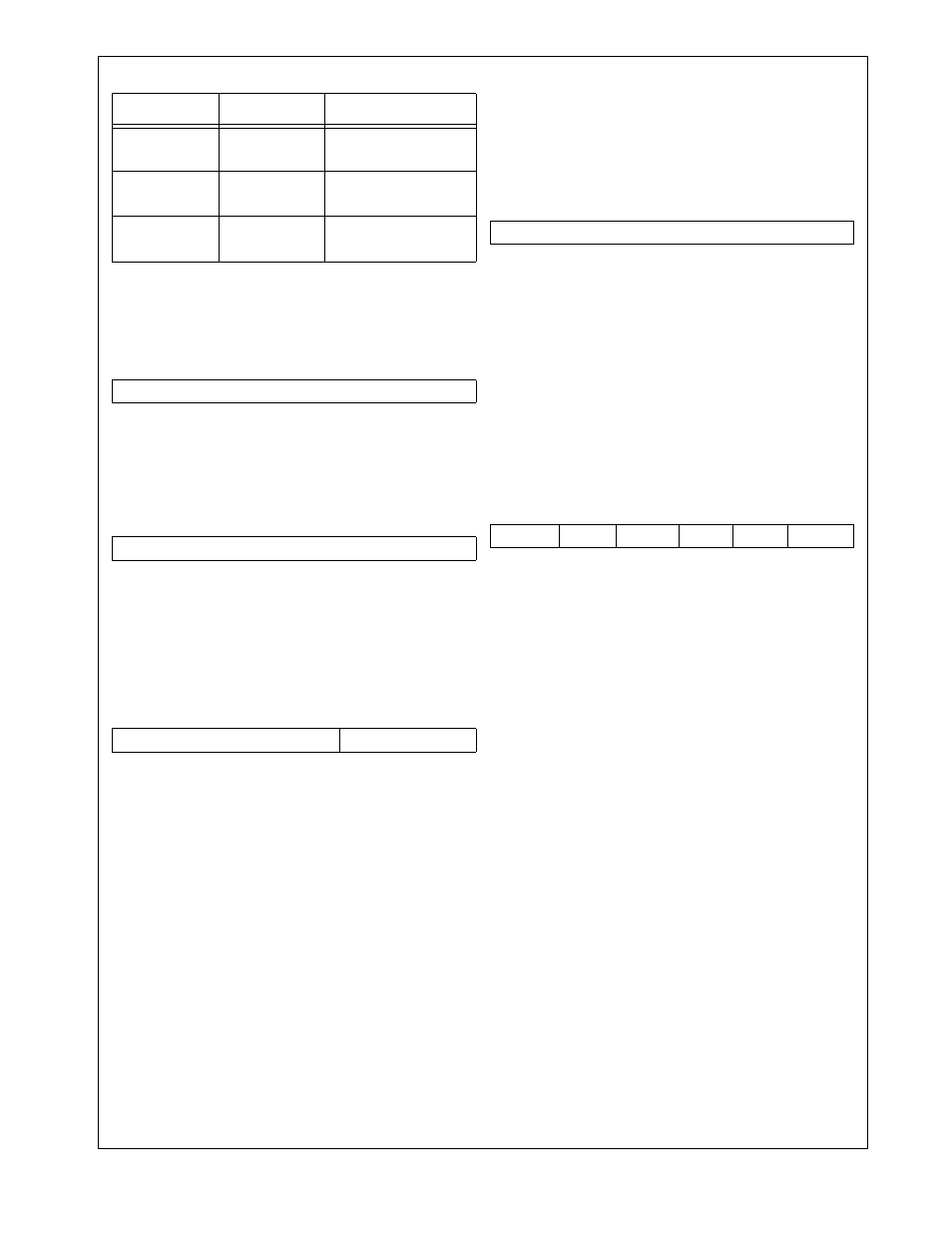

UART Receive Data Buffer (UnRBUF)

The UnRBUF register is a byte-wide, read/write register

used to receive each data byte.

22.3.2

UART Transmit Data Buffer (UnTBUF)

The UnTBUF register is a byte-wide, read/write register

used to transmit each data byte.

22.3.3

UART Baud Rate Prescaler (UnPSR)

The UnPSR register is a byte-wide, read/write register that

contains the 5-bit clock prescaler and the upper three bits of

the baud rate divisor. This register is cleared upon reset.

The register format is shown below.

UPSC

The Prescaler field specifies the prescaler val-

ue used for dividing the System Clock in the

first stage of the two-stage divider chain. For

the prescaler factors corresponding to each 5-

bit value, see Table 69.

UDIV10:8

The Baud Rate Divisor field holds the three

most significant bits (bits 10, 9, and 8) of the

UART baud rate divisor used in the second

stage of the two-stage divider chain. The re-

maining bits of the baud rate divisor are held

in the UnBAUD register.

22.3.4

UART Baud Rate Divisor (UnBAUD)

The UnBAUD register is a byte-wide, read/write register that

contains the lower eight bits of the baud rate divisor. The

register contents are unknown at power-up and are left un-

changed by a reset operation. The register format is shown

below.

UDIV7:0

The Baud Rate Divisor field holds the eight

lowest-order bits of the UART baud rate divi-

sor used in the second stage of the two-stage

divider chain. The three most significant bits

are held in the UnPSR register. The divisor

value used is (UDIV[10:0] + 1).

22.3.5

UART Frame Select Register (UnFRS)

The UnFRS register is a byte-wide, read/write register that

controls the frame format, including the number of data bits,

number of stop bits, and parity type. This register is cleared

upon reset. The register format is shown below.

UCHAR

The Character Frame Format field selects the

number of data bits per frame, not including

the parity bit, as follows:

00 – 8 data bits per frame.

01 – 7 data bits per frame.

10 – 9 data bits per frame.

11 – Loop-back mode, 9 data bits per frame.

USTP

The Stop Bits bit specifies the number of stop

bits transmitted in each frame. If this bit is 0,

one stop bit is transmitted. If this bit is 1, two

stop bits are transmitted.

0 – One stop bit per frame.

1 – Two stop bits per frame.

UXB9

The Transmit 9th Data Bit holds the value of

the ninth data bit, either 0 or 1, transmitted

when the UART is configured to transmit nine

data bits per frame. It has no effect when the

UART is configured to transmit seven or eight

data bits per frame.

UPSEL

The Parity Select field selects the treatment of

the parity bit. When the UART is configured to

transmit nine data bits per frame, the parity bit

is omitted and the UPSEL field is ignored.

00 – Odd parity.

01 – Even parity.

10 – No parity, transmit 1 (mark).

11 – No parity, transmit 0 (space).

U3OVR

FF F270h

UART3 Oversample

Rate Register

U3MDSL2

FF F272h

UART3 Mode Select

Register 2

U3SPOS

FF F274h

UART3 Sample

Position Register

7

0

URBUF

7

0

UnTBUF

7

3

2

0

UPSC

UDIV10:8

Table 70

UART Registers

Name

Address

Description

7

0

UDIV7:0

7

6

5

4

3

2

1

0

Reserved

UPEN

UPSEL

UXB9

USTP

UCHAR