2 vtu registers, Vtu registers, Cp3bt26 – National CP3BT26 User Manual

Page 210

www.national.com

210

CP3BT26

27.2

VTU REGISTERS

The VTU contains a total of 19 user accessible registers, as

listed in Table 81. All registers are word-wide and are initial-

ized to a known value upon reset. All software accesses to

the VTU registers must be word accesses.

27.2.1

Mode Control Register (MODE)

The MODE register is a word-wide read/write register which

controls the mode selection of all four timer subsystems.

The register is clear after reset.

TxRUN

The Timer Run bit controls whether the corre-

sponding timer is stopped or running. If set,

the associated counter and clock prescaler is

started depending on the mode of operation.

Once set, the clock to the clock prescaler and

the counter are enabled and the counter will

increment each time the clock prescaler

counter value matches the value defined in

the associated clock prescaler field (CxPR-

SC).

0 – Timer stopped.

1 – Timer running.

TMODx

The Timer System Operating Mode field en-

ables or disables the Timer Subsystem and

defines its operating mode.

00 – Low-Power Mode. All clocks to the

counter subsystem are stopped. The

counter is stopped regardless of the val-

ue of the TxRUN bits. Read operations

to the Timer Subsystem will return the

last value; software must not perform

any write operations to the Timer Sub-

system while it is disabled since those

will be ignored.

01 – Dual 8-bit PWM mode. Each 8-bit

counter may individually be started or

stopped via its associated TxRUN bit.

The TIOx pins will function as PWM out-

puts.

10 – 16-bit PWM mode. The two 8-bit

counters are concatenated to form a sin-

gle 16-bit counter. The counter may be

started or stopped with the lower of the

two TxRUN bits, i.e. T1RUN, T3RUN,

T5RUN, and T7RUN. The TIOx pins will

function as PWM outputs.

11 – Capture Mode. Both 8-bit counters are

concatenated and operate as a single

16-bit counter. The counter may be start-

ed or stopped with the lower of the two

TxRUN bits, i.e., T1RUN, T3RUN,

T5RUN, and T7RUN. The TIOx pins will

function as capture inputs.

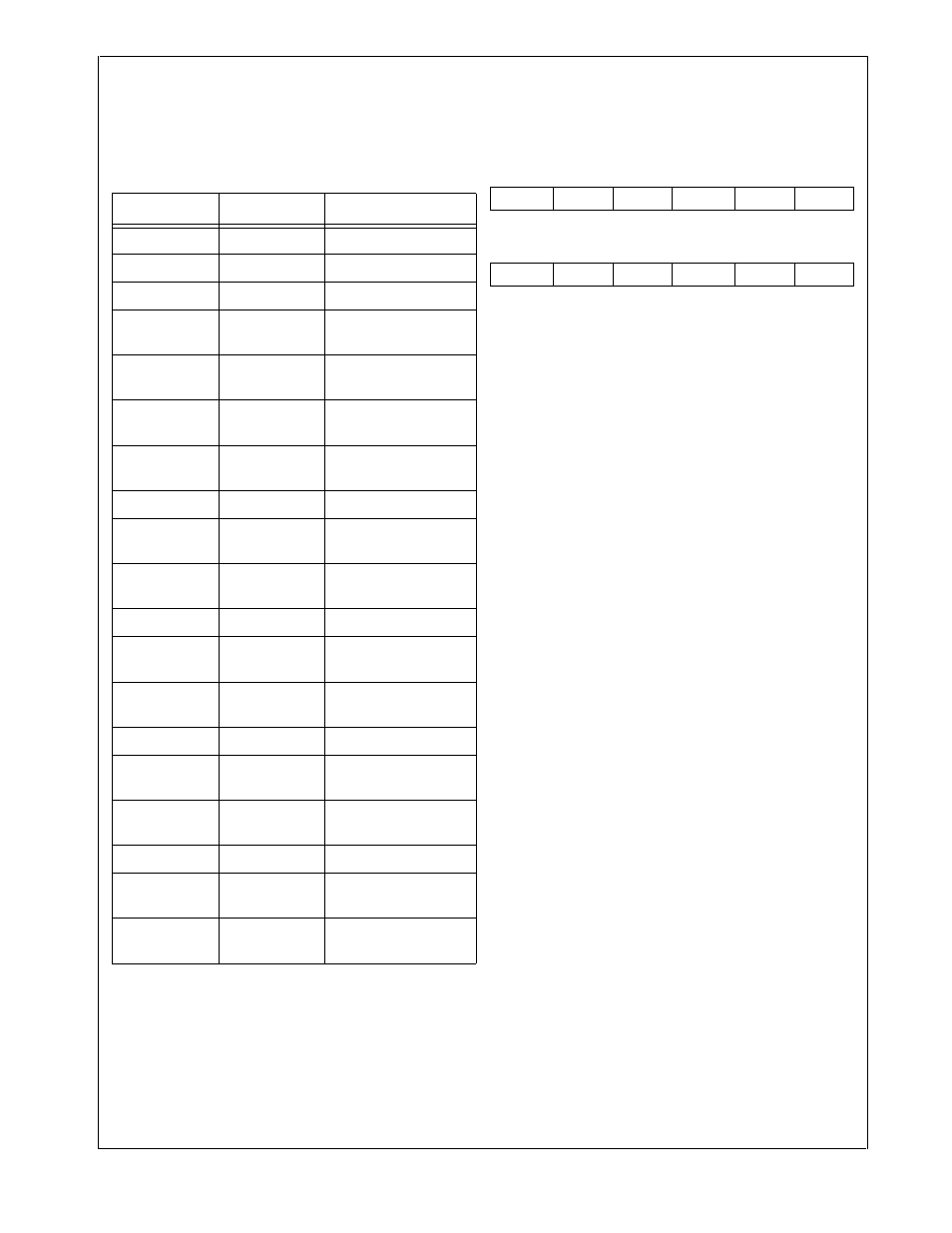

Table 81

VTU Registers

Name

Address

Description

MODE

FF FF80h

Mode Control Register

IO1CTL

FF FF82h

I/O Control Register 1

IO2CTL

FF FF84h

I/O Control Register 2

INTCTL

FF FF86h

Interrupt Control

Register

INTPND

FF FF88h

Interrupt Pending

Register

CLK1PS

FF FF8Ah

Clock Prescaler

Register 1

CLK2PS

FF FF98h

Clock Prescaler

Register 2

COUNT1

FF FF8Ch

Counter 1 Register

PERCAP1

FF FF8Eh

Period/Capture 1

Register

DTYCAP1

FF FF90h

Duty Cycle/Capture 1

Register

COUNT2

FF FF92h

Counter 2 Register

PERCAP2

FF FF94h

Period/Capture 2

Register

DTYCAP2

FF FF96h

Duty Cycle/Capture 2

Register

COUNT3

FF FF9Ah

Counter 3 Register

PERCAP3

FF FF9Ch

Period/Capture 3

Register

DTYCAP3

FF FF9Eh

Duty Cycle/Capture 3

Register

COUNT4

FF FFA0h

Counter 4 Register

PERCAP4

FF FFA2h

Period/Capture 4

Register

DTYCAP4

FF FFA4h

Duty Cycle/Capture 4

Register

7

6

5

4

3

2

1

0

TMOD2

T4RUN

T3RUN

TMOD1

T2RUN

T1RUN

15

14

13

12

11

10

9

8

TMOD4

T8RUN

T7RUN

TMOD3

T6RUN

T5RUN