0 dma controller, 1 channel assignment, 2 transfer types – National CP3BT26 User Manual

Page 41: Dma controller, Channel assignment, Transfer types, Cp3 bt26

41

www.national.com

CP3

BT26

9.0

DMA Controller

The DMA Controller (DMAC) has a register-based program-

ming interface, as opposed to an interface based on I/O

control blocks. After loading the registers with source and

destination addresses, as well as block size and type of op-

eration, a DMAC channel is ready to respond to DMA trans-

fer requests. A request can only come from on-chip

peripherals or software, not external peripherals. On receiv-

ing a DMA transfer request, if the channel is enabled, the

DMAC performs the following operations:

1. Arbitrates to become master of the CPU bus.

2. Determines priority among the DMAC channels, one

clock cycle before T1 of the DMAC transfer cycle. (T1

is the first clock cycle of the bus cycle.) Priority among

the DMAC channels is fixed in descending order, with

Channel 0 having the highest priority.

3. Executes data transfer bus cycle(s) selected by the val-

ues held in the control registers of the channel being

serviced, and according to the accessed memory ad-

dress. The DMAC acknowledges the request during the

bus cycle that accesses the requesting device.

4. If the transfer of a block is terminated, the DMAC does

the following:

Updates the termination bits.

Generates an interrupt (if enabled).

Goes to step 6.

5. If DMRQn is still active, and the Bus Policy is “continu-

ous”, returns to step 3.

6. Returns mastership of the CPU bus to the CPU.

Each DMAC channel can be programmed for direct (flyby)

or indirect (memory-to-memory) data transfers. Once a

DMAC transfer cycle is in progress, the next transfer request

is sampled when the DMAC acknowledge is de-asserted,

then on the rising edge of every clock cycle.

The configuration of either address freeze or address up-

date (increment or decrement) is independent of the num-

ber of transferred bytes, transfer direction, or number of

bytes in each DMAC transfer cycle. All these can be config-

ured for each channel by programming the appropriate con-

trol registers.

Each DMAC channel has eight control registers. DMAC

channels are described hereafter with the suffix n, where n

= 0 to 3, representing the channel number in the register-

names.

9.1

CHANNEL ASSIGNMENT

Table 17 shows the assignment of the DMA channels to dif-

ferent tasks. Four channels can be shared by a primary and

an secondary function. However, only one source at a time

can be enabled. If a channel is used for memory block trans-

fers, other resources must be disabled.

Table 17

DMA Channel Assignment

9.2

TRANSFER TYPES

The DMAC uses two data transfer modes, Direct (Flyby)

and Indirect (Memory-to-Memory). The choice of mode de-

pends on the required bus performance and whether direct

mode is available for the transfer. Indirect mode must be

used when the source and destination have differing bus

widths, when both the source and destination are in memo-

ry, and when the destination does not support direct mode.

9.2.1

Direct (Flyby) Transfers

In direct mode each data item is transferred using a single

bus cycle, without reading the data into the DMAC. It pro-

vides the fastest transfer rate, but it requires identical source

and destination bus widths. The DMAC cannot use Direct

cycles between two memory devices. One of the devices

must be an I/O device that supports the Direct (Flyby) mech-

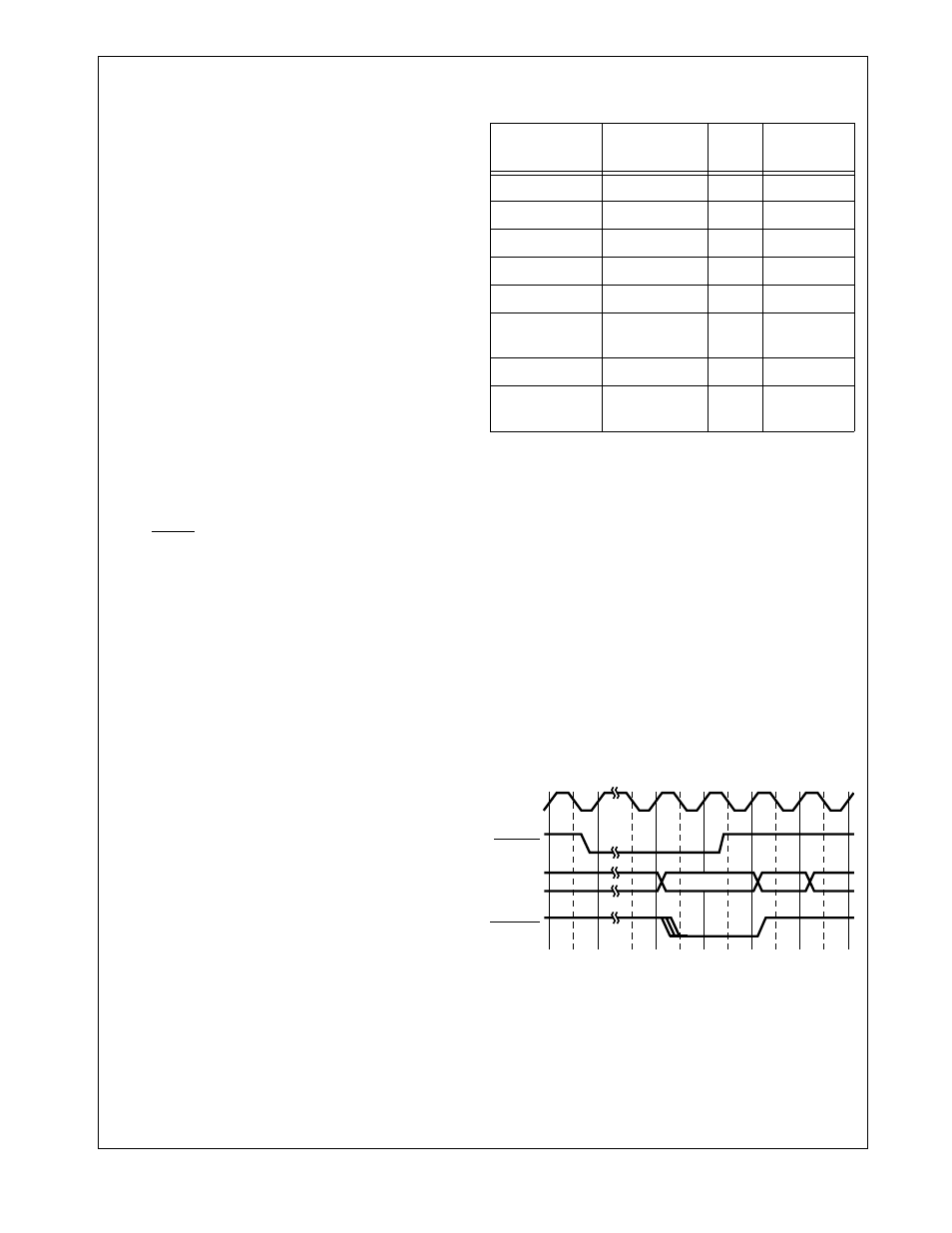

anism, as shown in Figure 3.

Figure 3.

Direct DMA Cycle Followed by a CPU Cycle

Channel

Peripheral

Trans-

action

Register

0 (Primary)

USB

R/W

RX/TX FIFO

0 (Secondary)

UART0

R

RXBUF

1 (Primary)

UART0

W

TXBUF

1 (Secondary)

Reserved

N/A

N/A

2 (Primary)

Audio Interface

R

ARDR0

2 (Secondary)

CVSD/PCM

Transcoder

R

PCMOUT

3 (Primary)

Audio Interface

W

ATDR0

3 (Secondary)

CVSD/PCM

Transcoder

W

PCMIN

DMRQ[3:0]

ADDR

ADCA

CLK

Bus State

T1

T1

T2

Tidle

DMACK[3:0]

DS005