Cp3bt26 – National CP3BT26 User Manual

Page 150

www.national.com

150

CP3BT26

20.6.4

IOM-2 Mode

The AAI can operate in a special IOM-2 compatible mode to

allow to connect to an external ISDN controller device. In

this IOM-2 mode, the AAI can only operate as a slave, i.e.

the bit clock and frame sync signal is provided by the ISDN

controller. The AAI only supports the B1 and B2 data of the

IOM-2 channel 0, but ignores the other two IOM-2 channels.

The AAI handles the B1 and B2 data as one 16-bit data

word.

The IOM-2 interface has the following properties:

Bit clock of 1536 kHz (output from the ISDN controller)

Frame repetition rate of 8 ksps (output from the ISDN

controller)

Double-speed bit clock (one data bit is two bit clocks

wide)

B1 and B2 data use 8-bit log PCM format

Long frame sync pulse

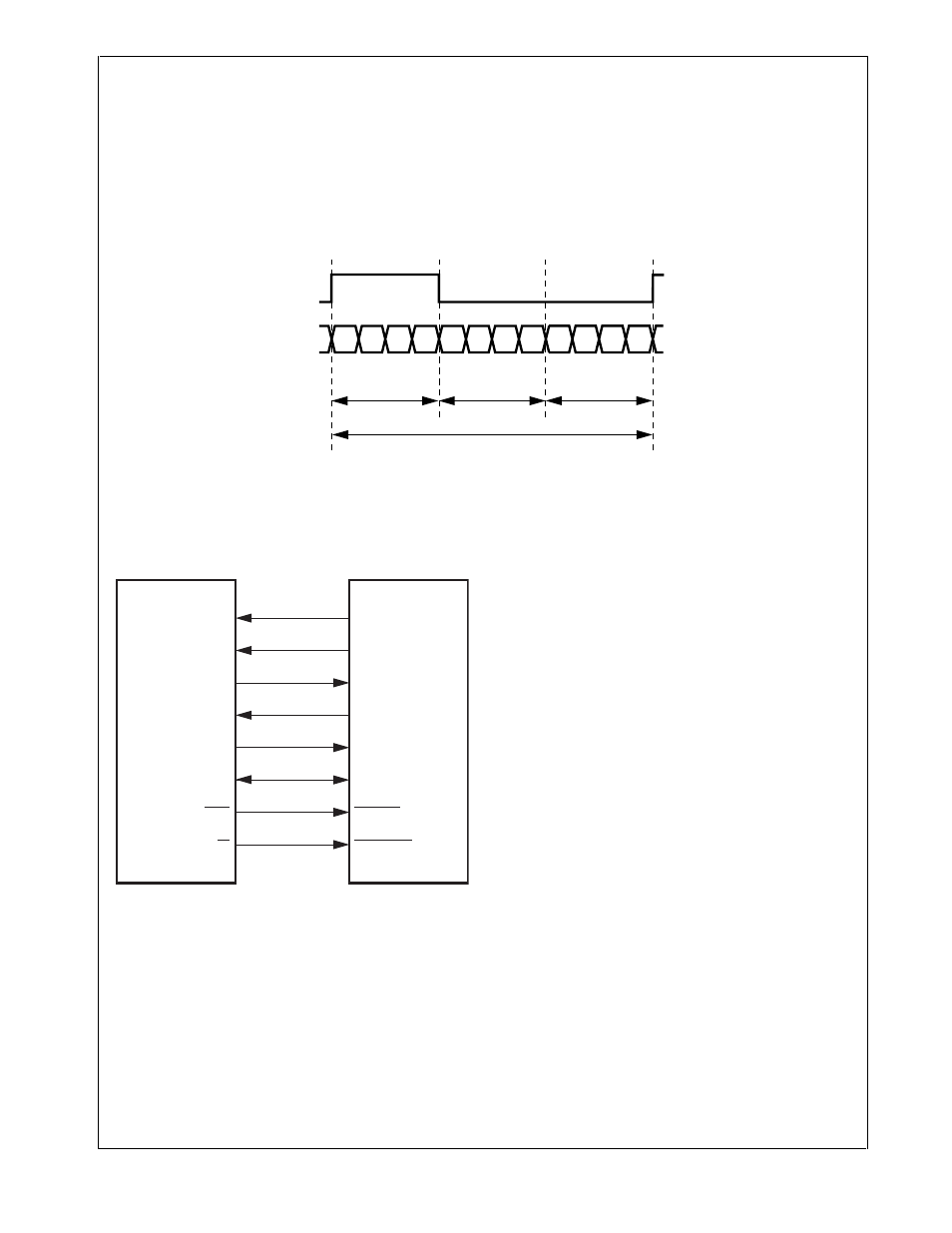

Figure 73 shows the structure of an IOM-2 Frame.

Figure 73.

IOM-2 Frame Structure

Figure 74 shows the connections between an ISDN control-

ler and a CP3BT26 using a standard IOM-2 interface for the

B1/B2 data communication and the external bus interface

(IO Expansion) for controlling the ISDN controller.

Figure 74.

CP3BT26/ISDN Controller Connections

To connect the AAI to an ISDN controller through an IOM-2

compatible interface, the AAI needs to be configured in this

way:

The AAI must be in IOM-2 Mode (AGCR.IOM2 = 1).

The AAI operates in synchronous mode (AGCR.ASS =

0).

The AAI operates as a slave, therefore the bit clock and

frame sync source selection must be set to external

(ACGR.IEFS = 1, ACGR.IEBC = 1).

The frame sync length must be set to long frame sync

(ACGR.FSS = 1).

The data word length must be set to 16-bit (AGCR.DWL

= 1).

The AAI must be set to normal mode (AGCR.SCS[1:0] =

0).

The internal frame rate must be 8 ksps (ACCR = 00BE).

20.6.5

Loopback Mode

In loopback mode, the STD and SRD pins are internally

connected together, so data shifted out through the ATSR

register will be shifted into the ARSR register. This mode

may be used for development, but it also allows testing the

transmit and receive path without external circuitry, for ex-

ample during Built-In-Self-Test (BIST).

C

M

IC2

IC1

C

M

B2

B1

STD/SRD

DS162

SFS

C

IOM-2 Channel 0

IOM-2 Frame (125 µs)

IOM-2 Channel 1

IOM-2 Channel 2

CP3BT2

x

ISDN C

ontroller

SCK

Bit Clock

DS241

SFS

Frame Sync

STD

Data In

SRD

Data Out

A[7:0]

Address

D[7:0]

Data

SELIO

Chip Select

RD

Output Enable