Cp3bt26 – National CP3BT26 User Manual

Page 186

www.national.com

186

CP3BT26

NEGACK

The Negative Acknowledge bit is set by hard-

ware when a transmission is not acknowl-

edged on the ninth clock. (In this case, the

SDAST bit is not set.) Writing 1 to NEGACK

clears it. It is also cleared when the module is

disabled. Writing 0 to the NEGACK bit is ig-

nored.

0 – No transmission not acknowledged condi-

tion.

1 – Transmission not acknowledged.

BER

The Bus Error bit is set by the hardware when

a Start or Stop Condition is detected during

data transfer (i.e., Start or Stop Condition dur-

ing the transfer of bits 2 through 8 and ac-

knowledge cycle), or when an arbitration

problem is detected. Writing 1 to the BER bit

clears it. It is also cleared when the module is

disabled. Writing 0 to the BER bit is ignored.

0 – No bus error occurred.

1 – Bus error occurred.

SDAST

The SDA Status bit indicates that the SDA

data register is waiting for data (transmit, as

master or slave) or holds data that should be

read (receive, as master or slave). This bit is

cleared when reading from the ACBSDA reg-

ister during a receive, or when written to dur-

ing a transmit. When the ACBCTL1.START bit

is set, reading the ACBSDA register does not

clear the SDAST bit. This enables the ACB to

send a repeated start in master receive mode.

0 – ACB module is not waiting for data trans-

fer.

1 – ACB module is waiting for data to be load-

ed or unloaded.

SLVSTP

The Slave Stop bit indicates that a Stop Con-

dition was detected after a slave transfer (i.e.,

after a slave transfer in which MATCH or

GCMATCH is set). Writing 1 to SLVSTP clears

it. It is also cleared when the module is dis-

abled. Writing 0 to SLVSTP is ignored.

0 – No stop condition after slave transfer oc-

curred.

1 – Stop condition after slave transfer oc-

curred.

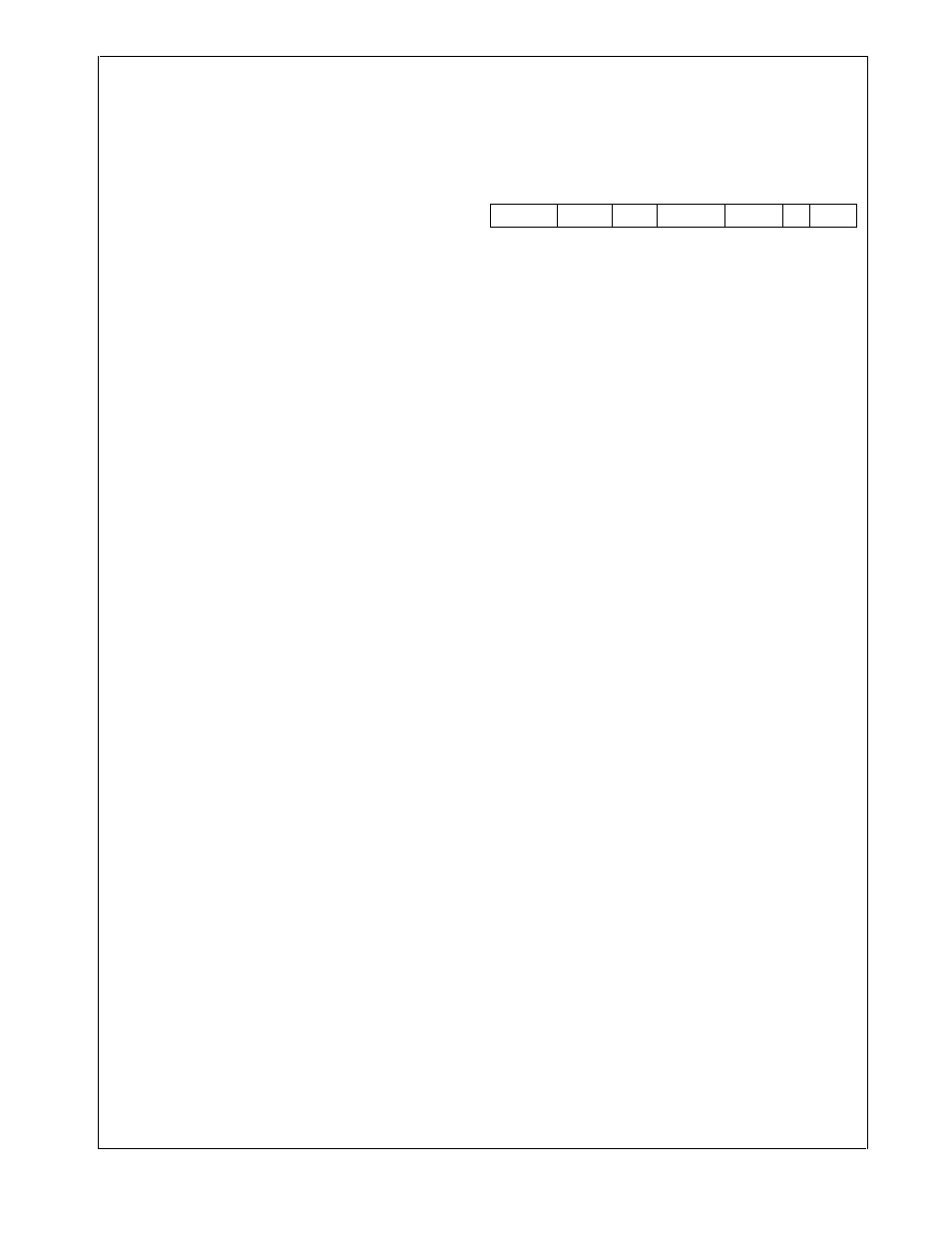

24.3.3

ACB Control Status Register (ACBCST)

The ACBCST register is a byte-wide, read/write register that

maintains current ACB status. At reset and when the mod-

ule is disabled, the non-reserved bits of ACBCST are

cleared.

BUSY

The BUSY bit indicates that the ACB module

is:

Generating a Start Condition

In Master mode (ACBST.MASTER is set)

In Slave mode (ACBCST.MATCH or

ACBCST.GCMTCH is set)

In the period between detecting a Start

and completing the reception of the ad-

dress byte. After this, the ACB either be-

comes not busy or enters slave mode.

The BUSY bit is cleared by the completion of

any of the above states, and by disabling the

module. BUSY is a read only bit. It must al-

ways be written with 0.

0 – ACB module is not busy.

1 – ACB module is busy.

BB

The Bus Busy bit indicates the bus is busy. It

is set when the bus is active (i.e., a low level

on either SDA or SCL) or by a Start Condition.

It is cleared when the module is disabled, on

detection of a Stop Condition, or when writing

1 to this bit. See “Usage Hints” on page 189

for a description of the use of this bit. This bit

should be set when either the SDA or SCL sig-

nals are low. This is done by sampling the

SDA and SCL signals continuously and set-

ting the bit if one of them is low. The bit re-

mains set until cleared by a STOP condition or

written with 1.

0 – Bus is not busy.

1 – Bus is busy.

MATCH

The Address Match bit indicates in slave

mode when ACBADDR.SAEN is set and the

first seven bits of the address byte (the first

byte transferred after a Start Condition)

matches the 7-bit address in the ACBADDR

register, or when ACBADDR2.SAEN is set

and the first seven bits of the address byte

matches the 7-bit address in the ACBADDR2

register. It is cleared by Start Condition or re-

peated Start and Stop Condition (including il-

legal Start or Stop Condition).

0 – No address match occurred.

1 – Address match occurred.

7

6

5

4

3

2

1

0

Reserved TGSCL TSDA GCMTCH MATCH BB BUSY