Cp3bt26 – National CP3BT26 User Manual

Page 134

www.national.com

134

CP3BT26

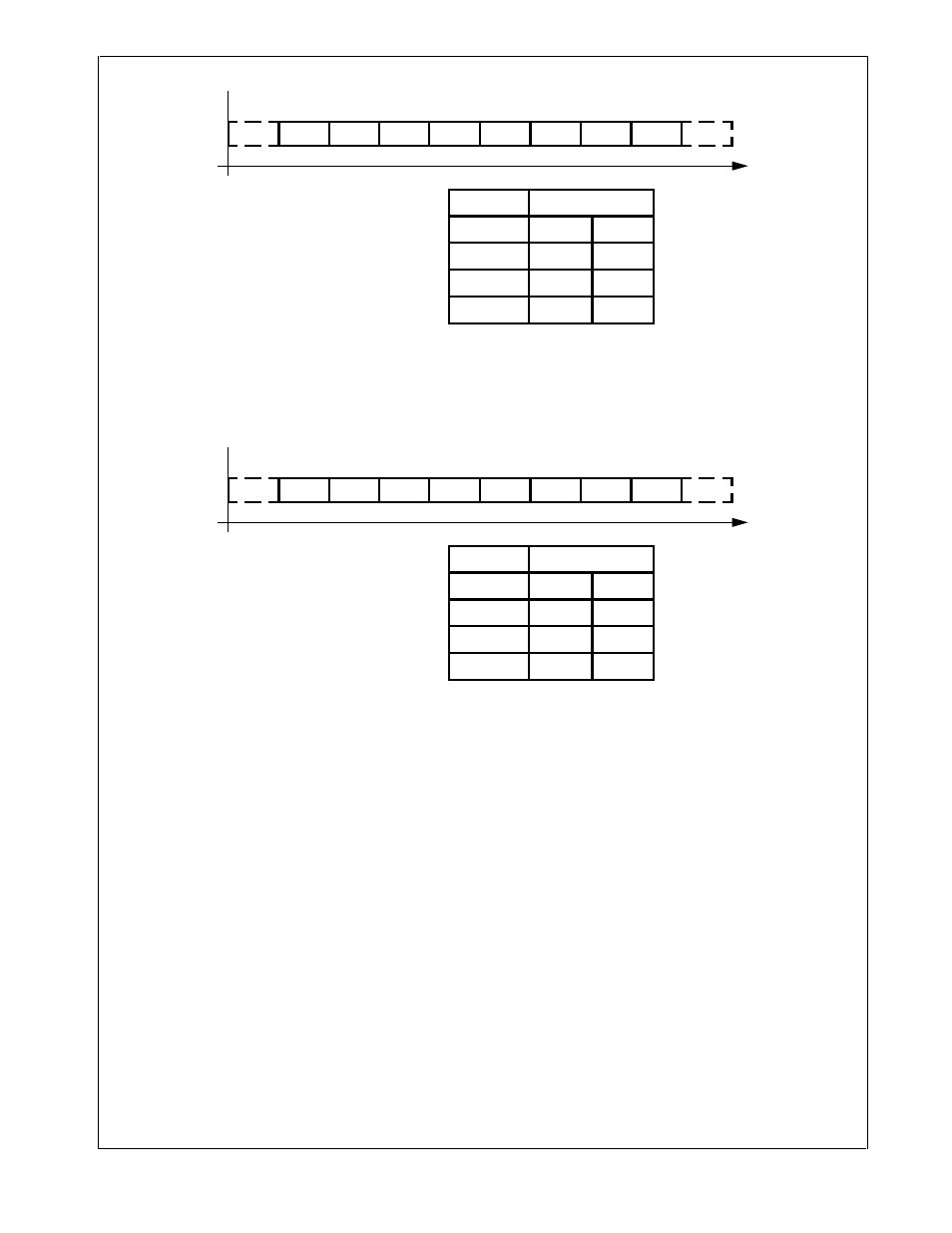

Figure 61.

Data Direction Bit Clear

Setting the DDIR bit will cause the direction of the data stor-

age to be reversed — the last byte received is stored at the

highest address and the first byte is stored at the lowest ad-

dress, as shown in Figure 62.

Figure 62.

Data Direction Bit Set

LO

The Listen Only bit can be used to configure

the CAN interface to behave only as a receiv-

er. This means:

•

Cannot transmit any message.

•

Cannot send a dominant ACK bit.

•

When errors are detected on the bus, the

CAN module will behave as in the error

passive mode.

Using this listen only function, the CAN inter-

face can be adjusted for connecting to an op-

erating network with unknown bus speed.

0 – Transmit/receive mode.

1 – Listen-only mode.

IGNACK

When the Ignore Acknowledge bit is set, the

CAN module does not expect to receive a

dominant ACK bit to indicate the validity of a

transmitted message. It will not send an error

frame when the transmitted frame is not ac-

knowledged by any other CAN node. This fea-

ture can be used in conjunction with the

LOOPBACK bit for stand-alone tests outside

of a CAN network.

0 – Normal mode.

1 – The CAN module does not expect to re-

ceive a dominant ACK bit to indicate the

validity of a transmitted message.

LOOPBACK

When the Loopback bit is set, all messages

sent by the CAN module can also be received

by a CAN module buffer with a matching buff-

er ID. However, the CAN module does not ac-

knowledge a message sent by itself.

Therefore, the CAN module will send an error

frame when no other device connected to the

bus has acknowledged the message.

0 – No loopback.

1 – Loopback enabled.

Storage of Data Bytes

in the Buffer Memory

Sequence of Data Bytes on the Bus

CRC

Data8

t

Data7

Data6

Data5

Data4

Data3

Data2

Data1

ID

Data2

Data1

0A

16

Data4

Data3

08

16

Data6

Data5

06

16

Data8

Data7

04

16

Data Bytes

ADDR Offset

DS045

Storage of Data Bytes

in the Buffer Memory

Sequence of Data Bytes on the Bus

CRC

Data8

t

Data7

Data6

Data5

Data4

Data3

Data2

Data1

ID

Data7

Data8

0A

16

Data5

Data6

08

16

Data3

Data4

06

16

Data1

Data2

04

16

Data Bytes

ADDR Offset

DS046