Cp3bt26 – National CP3BT26 User Manual

Page 102

www.national.com

102

CP3BT26

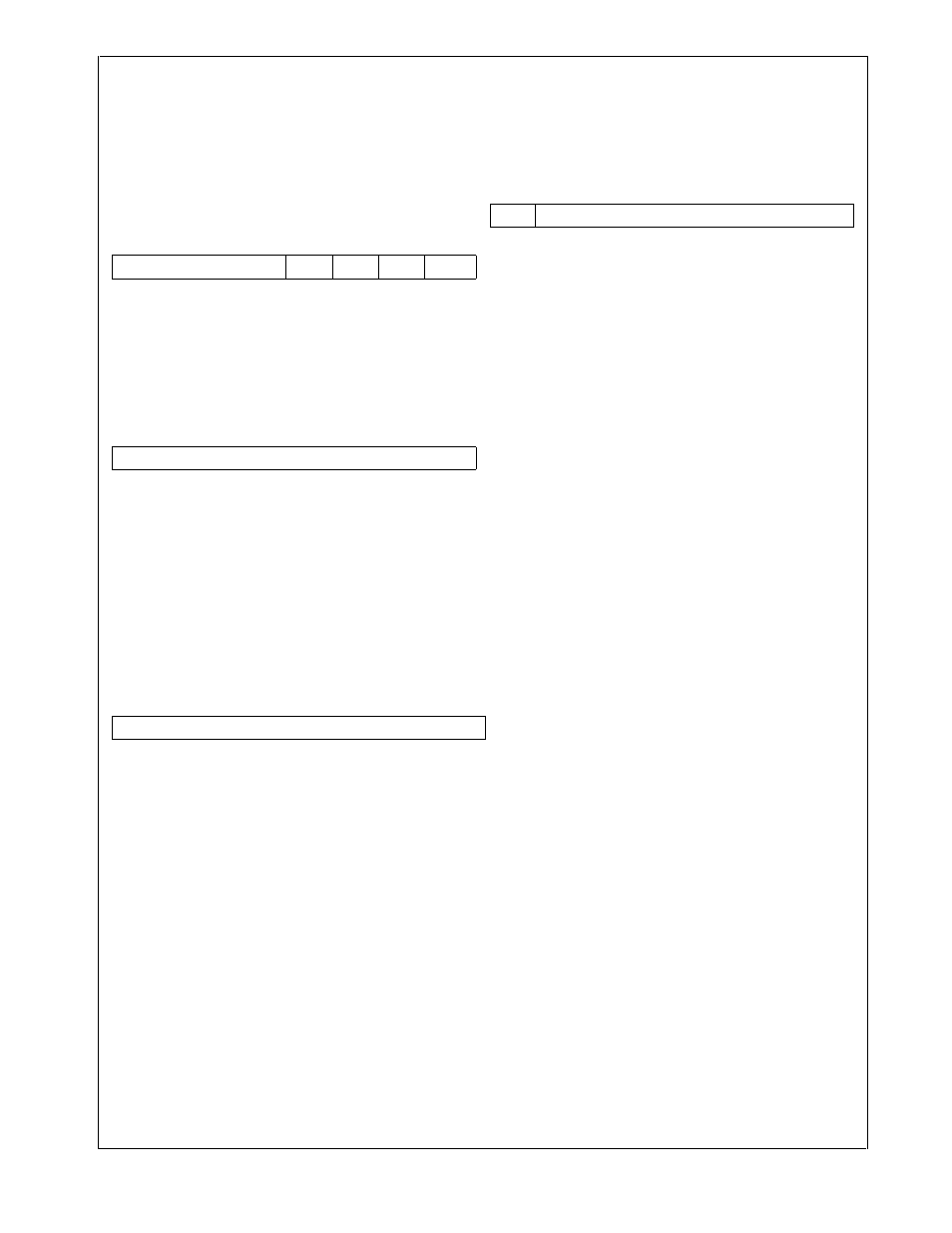

18.3.20 DMA Mask Register (DMAMSK)

Any set bit in the DMAMSK register enables automatic set-

ting of the DMA bit in the ALTEV register when the respec-

tive event in the DMAEV register occurs. Otherwise, setting

the DMA bit is disabled. For a description of bits 0 to 3, see

the DMAEV register. The DMAMSK register provides read/

write access. After reset it is clear. Reading reserved bits re-

turns undefined data.

18.3.21 Mirror Register (MIR)

The MIR register is a read-only register. Because reading it

does not alter the state of the TXSn or RXSn register to

which it points, software can freely check the status of the

channel. At reset it is initialized to 1Fh.

STAT

The Status field mirrors the status bits of the

transmitter or receiver n selected by the

DSRC[2:0] field in the DMACNTRL register

(DMA need not be active or enabled). It corre-

sponds to TXSn or RXSn, respectively.

18.3.22 DMA Count Register (DMACNT)

The DMACNT register specifies a maximum count for

ADMA operations. The DMACNT register provides read/

write access. After reset this register is clear.

DCOUNT

The DMA Count field is decremented on com-

pletion of a DMA operation until it reaches 0.

Then the DCNT bit in the DMA Event register

is set, only when the next successful DMA op-

eration is completed. This register does not

underflow. For receive operations, this count

decrements when the packet is received suc-

cessfully, and then transferred to memory us-

ing DMA. For transmit operations, this count

decrements when the packet is transferred

from memory using DMA, and then transmit-

ted successfully. Software loads DCOUNT

with (number of packets to transfer) - 1. If a

DMACNT write operation occurs simulta-

neously with the decrement operation, the

write takes precedence.

18.3.23 DMA Error Register (DMAERR)

The DMAERR register holds the 7-bit DMA error counter

and a control bit to specify DMA error handling. The DMAE-

RR register provides read/write access. It is clear after re-

set.

DMAERRCNT The DMA Error Counter, together with the au-

tomatic error handling feature, defines the

maximum number of consecutive bus errors

before ADMA mode is stopped. Software can

set the 7-bit counter to a preset value. Once

ADMA is started, the counter decrements

from the preset value by 1 every time a bus er-

ror is detected. Every successful transaction

resets the counter back to the preset value.

When ADMA mode is stopped, the counter is

also set back to the preset value. If the

counter reaches 0 and another erroneous

packet is detected, the DERR bit in the DMA

Event register is set. This register cannot un-

derrun. Software loads DMAERRCNT with 3D

(maximum number of allowable transfer at-

tempts) - 1. A write access to this register is

only possible when ADMA is inactive. Other-

wise, it is ignored. Reading from this register

while ADMA is active returns the current

counter value. Reading from it while ADMA is

inactive returns the preset value. The counter

decrements only if the AEH bit is set (auto-

matic error handling activated).

AEH

The Automatic Error Handling bit has two dif-

ferent meanings, depending on the current

mode:

Non-Isochronous mode

—

This mode is

used for bulk, interrupt and control trans-

fers. Setting AEH in this mode enables au-

tomatic handling of packets containing

CRC or bit-stuffing errors. If this bit is set

during transmit operations, the USB node

automatically reloads the FIFO and re-

schedules the packet to which the host did

not return an ACK. If this bit is clear, auto-

matic error handling ceases. If this bit is

set during receive operations, a packet re-

ceived with an error (as specified in the

DERR bit description in the DMAEV regis-

ter) is automatically flushed from the FIFO

being used so that the packet can be re-

ceived again. If this bit is cleared, auto-

matic error handling ceases.

Isochronous mode

—

Setting this bit al-

lows the USB node to ignore packets re-

ceived with errors (as specified in the

DERR bit description in the DMAMSK reg-

ister). If this bit is set during receive oper-

ations, the USB node is automatically

flushed and the receive FIFO is reset to

7

4

3

2

1

0

Reserved

DSIZ DCNT DERR DSHLT

7

0

STAT

7

0

DCOUNT

7

6

0

AEH

DMAERRCNT