0 cvsd/pcm conversion module, 1 operation, 2 pcm conversions – National CP3BT26 User Manual

Page 158: Cp3bt26

www.national.com

158

CP3BT26

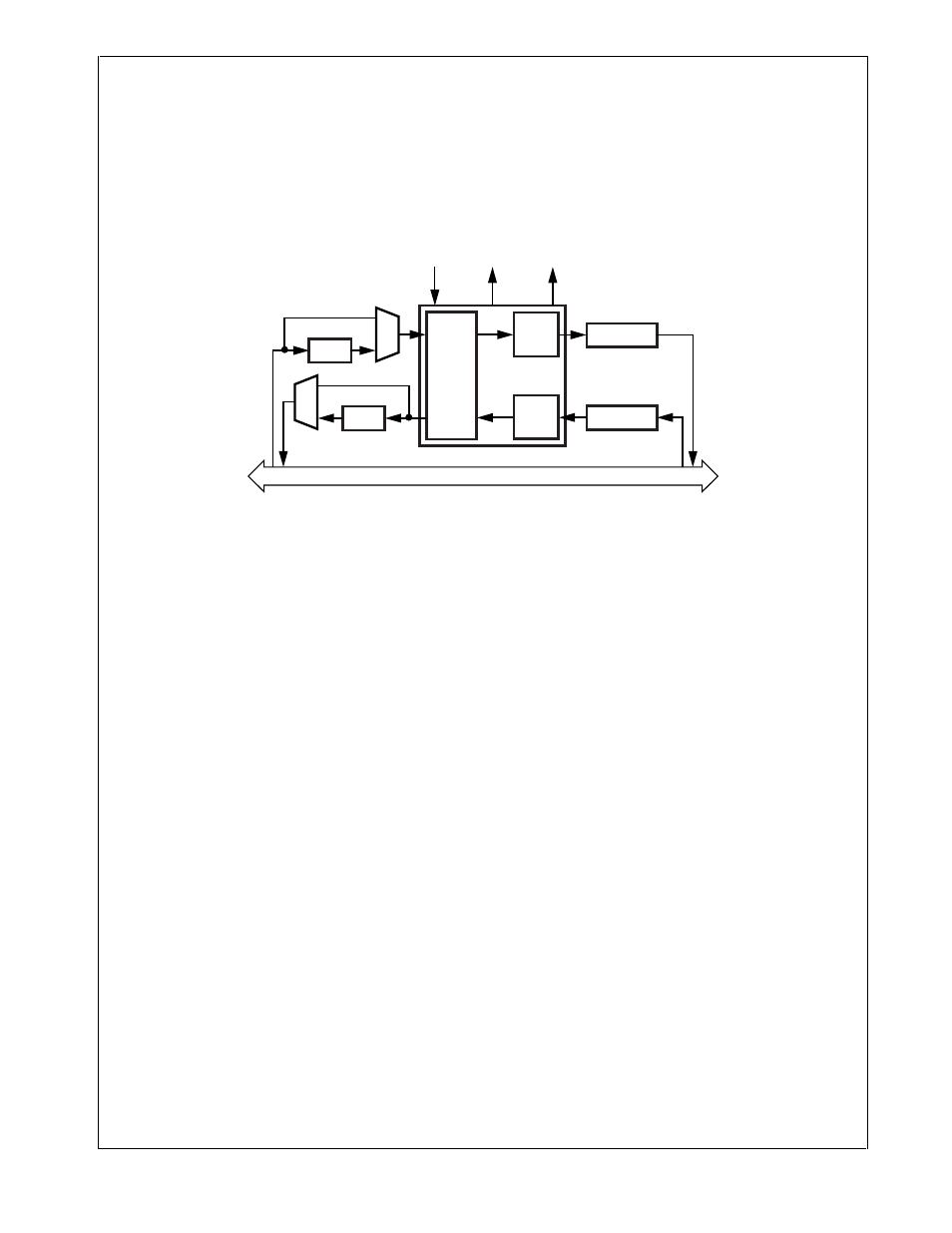

21.0 CVSD/PCM Conversion Module

The CVSD/PCM module performs conversion between

CVSD data and PCM data, in which the CVSD encoding is

as defined in the Bluetooth specification and the PCM en-

coding may be 8-bit µ-Law, 8-bit A-Law, or 13-bit to 16-bit

Linear.

The CVSD conversion module operates at a fixed rate of

125 µs (8 kHz) per PCM sample. On the CVSD side, there

is a read and a write FIFO allowing up to 8 words of data to

be read or written at the same time. On the PCM side, there

is a double-buffered register requiring data to be read and

written every 125 µs. The intended use is to move CVSD

data into the module with a CVSD interrupt handler, and to

move PCM data with DMA. Figure 75 shows a block dia-

gram of the CVSD to PCM module.

Figure 75.

CVSD/PCM Converter Block Diagram

21.1

OPERATION

The Aux2 clock (generated by the Clock module described

in Section 11.9) must be configured, because it drives the

CVSD module. Software must set its prescaler to provide a

2 MHz input clock based upon the System Clock (usually

12 MHz). This is done by writing an appropriate divisor to

the ACDIV2 field of the PRSAC register. Software must also

enable the Aux2 clock by setting the ACE2 bit within the

CRCTRL register. For example:

PRSAC &= 0x0f;

// Set Aux2 prescaler to generate

// 2 MHz (Fsys = 12 MHz)

PRSAC |= 0x50;

CRCTRL |= ACE2; // Enable Aux2 clk

The module converts between PCM data and CVSD data at

a fixed rate of 8 kHz per PCM sample. Due to compression,

the data rate on the CVSD side is only 4 kHz per CVSD

sample.

If PCM interrupts are enabled (PCMINT is set) every 125 µs

(8 kHz) an interrupt will occur and the interrupt handler can

operate on some or all of the four audio streams CVSD in,

CVSD out, PCM in, and PCM out. Alternatively, a DMA re-

quest is issued every 125 µs and the DMA controller is used

to move the PCM data between the CVSD/PCM module

and the audio interface.

If CVSD interrupts are enabled, an interrupt is issued when

either one of the CVSD FIFOs is almost empty or almost full.

On the PCM data side there is double buffering, and on the

CVSD side there is an eight word (8 × 16-bit) FIFO for the

read and write paths.

Inside the module, a filter engine receives the 8 kHz stream

of 16-bit samples and interpolates to generate a 64 kHz

stream of 16-bit samples. This goes into a CVSD encoder

which converts the data into a single-bit delta stream using

the CVSD parameters as defined by the Bluetooth specifi-

cation. There is a similar path that reverses this process

converting the CVSD 64 kHz bit stream into a 64 kHz 16-bit

data stream. The filter engine then decimates this stream

into an 8 kHz, 16-bit data stream.

21.2

PCM CONVERSIONS

During conversion between CVSD and PCM, any PCM for-

mat changes are done automatically depending on whether

the PCM data is µ-Law, A-Law, or Linear. In addition to this,

a separate function can be used to convert between the var-

ious PCM formats as required. Conversion is performed by

setting up the control bit CVCTL1.PCMCONV to define the

conversion and then writing to the LOGIN and LINEARIN

registers and reading from the LOGOUT and LINEAROUT

registers. There is no delay in the conversion operation and

it does not have to operate at a fixed rate. It will only convert

between µ-Law/A-Law and linear, not directly between µ-

Law and A-Law. (This could easily be achieved by convert-

ing between µ-Law and linear and between linear and A-

Law.)

If a conversion is performed between linear and µ-Law log

PCM data, the linear PCM data are treated in the left-

aligned 14-bit linear data format with the two LSBs unused.

If a conversion is performed between linear and A-Law log

PCM data, the linear PCM data are treated in the left-

aligned 13-bit linear data format with the three LSBs un-

used.

Peripheral Bus

Filter

Engine

16-Bit Shift Reg

1-Bit 64 kHz

1-Bit 64 kHz

16-Bit

16-Bit

64 kHz

64 kHz

16-Bit Shift Reg

16-Bit 8 kHz

CVSD

Encoder

DMA

Interrupt

2 MHz

Clock Input

CVSD

Decoder

u/A-Law

16-Bit 8 kHz

u/A-Law

DS058