Cp3 bt26 – National CP3BT26 User Manual

Page 145

145

www.national.com

CP3

BT26

On the receiver side, only the valid data bits which were re-

ceived during the slots assigned to this interface are copied

into the receive FIFO or DMA registers. The assignment of

slots to the receiver is specified by the Receive Slot Assign-

ment bits (RXSA) in the ATCR register. It can also be spec-

ified whether the received data is copied into the receive

FIFO or into the corresponding DMA receive register. There

is one DMA receive register (ARDRn) for each of the maxi-

mum four data slots. Each slot may be configured individu-

ally.

Figure 67 shows the frame timing while operating in network

mode with four slots per frame, slot 1 assigned to the inter-

face, and a long frame sync interval.

Figure 67.

Network Mode Frame

IRQ Support

If DMA is not enabled for a receive slot n (RXDSAn = 0), all

data received in this slot is loaded into the receive FIFO. An

IRQ is asserted as soon as the number of data bytes or

words in the receive FIFO is greater than a configured warn-

ing limit.

If DMA is not enabled for a transmit slot n (TXDSAn = 0), all

data to be transmitted in this slot are read from the transmit

FIFO. An IRQ is asserted as soon as the number data bytes

or words available in the transmit FIFO is equal or less than

a configured warning limit.

DMA Support

If DMA support is enabled for a receive slot n (RXDSA0 =

1), all data received in this slot is only transferred from the

ARSR into the corresponding DMA receive register

(ARDRn). A DMA request is asserted when the ARDRn reg-

ister is full.

If DMA is enabled for a transmit slot n (TXDSAn = 1), all data

to be transmitted in slot n are read from the corresponding

DMA transmit register (ATDRn). A DMA request is asserted

to the DMA controller when the ATDRn register is empty.

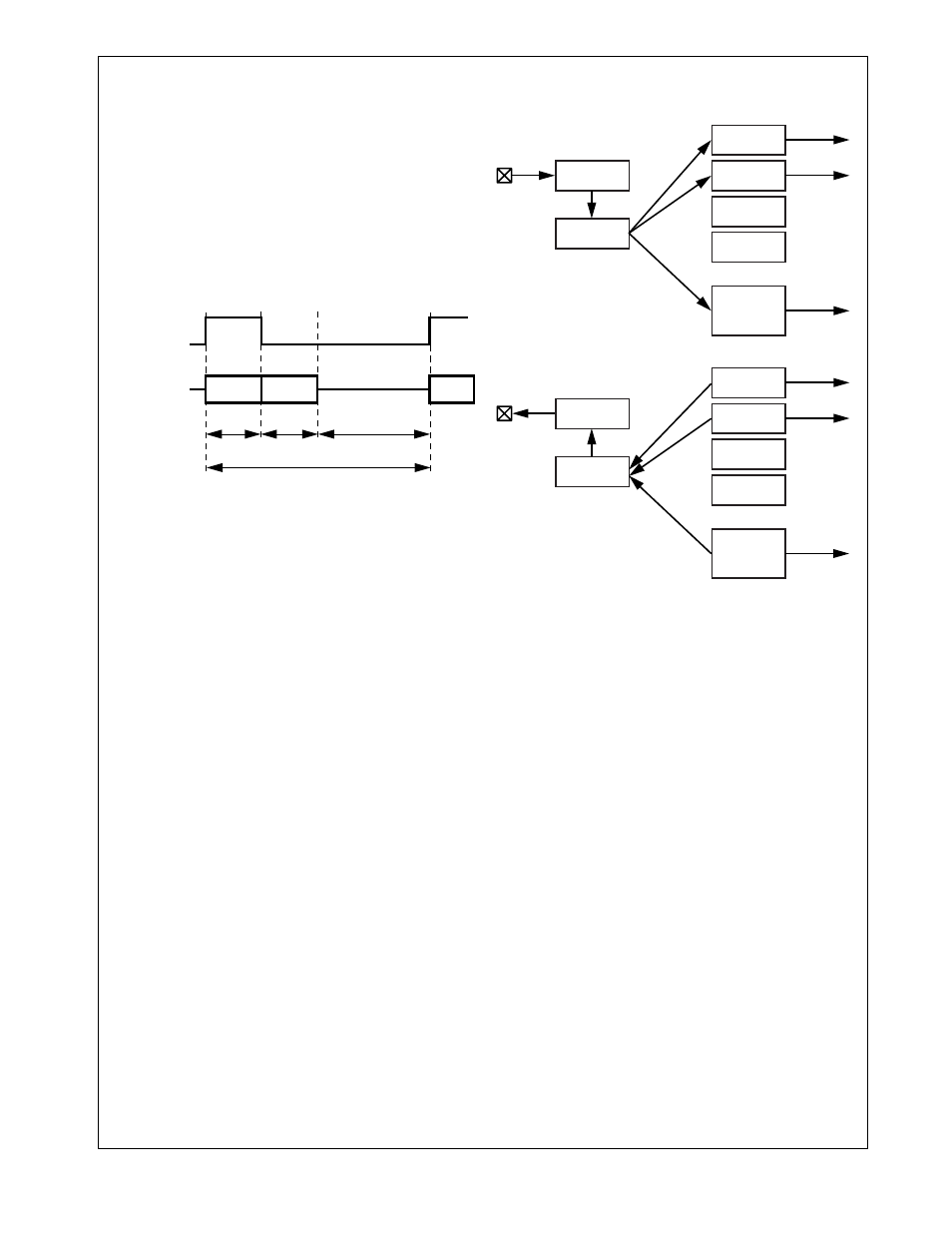

Figure 68 illustrates the data flow for IRQ and DMA support

in network mode, using four slots per frame and DMA sup-

port enabled for slots 0 and 1 in receive and transmit direc-

tion.

Figure 68.

IRQ/DMA Support in Network Mode

If the interface operates in synchronous mode, the receiver

uses the transmit bit clock (SCK) and transmit frame sync

signal (SFS). This allows the pins used for the receive bit

clock (SRCLK) and receive frame sync (SRFS) to be used

as additional frame sync signals in network mode. The extra

frame sync signals are useful when the audio interface com-

municates to more than one codec, because codecs typical-

ly start transmission immediately after the frame sync pulse.

The SRCLK pin is driven with a frame sync pulse at the be-

ginning of the second slot (slot 1), and the SRFS pin is driv-

en with a frame sync pulse at the beginning of slot 2.

Figure 69 shows a frame timing diagram for this configura-

tion, using the additional frame sync signals on SRCLK and

SRFS to address up to three devices.

Shift Data

(STD/SRD)

High-impedance

Unused Slots

Slot1

Frame

Slot0

Long Frame Sync

(SFS/SRFS)

Data

(ignored)

Data

(ignored)

Data

(valid)

DS055

DMA Slot

Assignment

Slot 1 data

Slot 0 data

Slot 2 and 3 data

ARSR

SRD

ARDR 0

DMA

Request 1

ARDR 1

DMA

Request 3

ARDR 2

ARDR 3

RX

FIFO

IRQ

DMA Slot

Assignment

Slot 1 data

Slot 0 data

ATSR

STD

ATDR 0

DMA

Request 0

ATDR 1

DMA

Request 2

ATDR 2

ATDR 3

TX

FIFO

IRQ

Slot 2 and 3 data

DS056