Cp3 bt26 – National CP3BT26 User Manual

Page 211

211

www.national.com

CP3

BT26

27.2.2

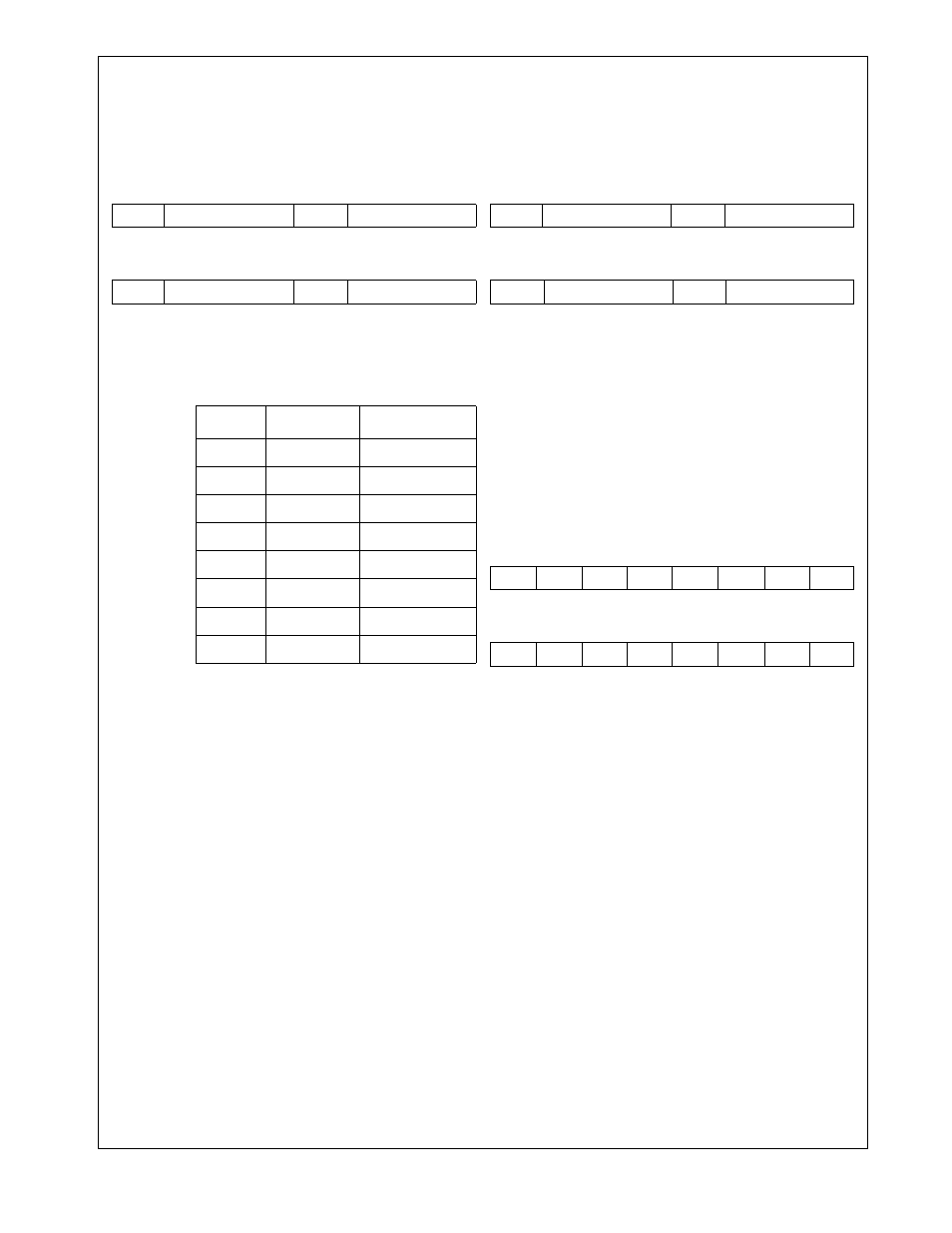

I/O Control Register 1 (IO1CTL)

The I/O Control Register 1 (IO1CTL) is a word-wide read/

write register. The register controls the function of the I/O

pins TIO1 through TIO4 depending on the selected mode of

operation. The register is clear after reset.

CxEDG

The Capture Edge Control field specifies the

polarity of a capture event and the reset of the

counter. The value of this three bit field has no

effect while operating in PWM mode.

PxPOL

The PWM Polarity bit selects the output polar-

ity. While operating in PWM mode the bit

specifies the polarity of the corresponding

PWM output (TIOx). Once a counter is

stopped, the output will assume the value of

PxPOL, i.e., its initial value. The PxPOL bit

has no effect while operating in capture mode.

0 – The PWM output goes high at the 00h to

01h transition of the counter and will go

low once the counter value matches the

duty cycle value.

1 – The PWM output goes low at the 00h to

01h transition of the counter and will go

high once the counter value matches the

duty cycle value.

27.2.3

I/O Control Register 2 (IO2CTL)

The IO2CTL register is a word-wide read/write register. The

register controls the functionality of the I/O pins TIO5

through TIO8 depending on the selected mode of operation.

The register is cleared at reset.

The functionality of the bit fields of the IO2CTL register is

identical to the ones described in the IO1CTL register sec-

tion.

27.2.4

Interrupt Control Register (INTCTL)

The INTCTL register is a word-wide read/write register. It

contains the interrupt enable bits for all 16 interrupt sources

of the VTU. Each interrupt enable bit corresponds to an in-

terrupt pending bit located in the Interrupt Pending Register

(INTPND). All INTCTL register bits are solely under soft-

ware control. The register is clear after reset.

IxAEN

The Timer x Interrupt A Enable bit controls in-

terrupt requests triggered on the correspond-

ing IxAPD bit being set. The associated

IxAPD bit will be updated regardless of the

value of the IxAEN bit.

0 – Disable system interrupt request for the

IxAPD pending bit.

1 – Enable system interrupt request for the Ix-

APD pending bit.

IxBEN

The Timer x Interrupt B Enable bit controls in-

terrupt requests triggered on the correspond-

ing IxBPD bit being set. The associated

IxBPD bit will be updated regardless of the

value of the IxBEN bit.

0 – Disable system interrupt request for the

IxBPD pending bit.

1 – Enable system interrupt request for the Ix-

BPD pending bit.

7

6

4

3

2

0

P2POL

C2EDG

P1POL

C1EDG

15

14

12

11

10

8

P4POL

C4EDG

P3POL

C3EDG

CxEDG

Capture

Counter Reset

000

Rising edge

No

001

Falling edge

No

010

Rising edge

Yes

011

Falling edge

Yes

100

Both edges

No

101

Both edges

Rising edge

110

Both edges

Falling edge

111

Both edges

Both edges

7

6

4

3

2

0

P6POL

C6EDG

P5POL

C5EDG

15

14

12

11

10

8

P8POL

C8EDG

P7POL

C7EDG

7

6

5

4

3

2

1

0

I2DEN I2CEN I2BEN I2AEN I1DEN I1CEN I1BEN I1AEN

15

14

13

12

11

10

9

8

I4DEN I4CEN I4BEN I4AEN I3DEN I3CEN I3BEN I3AEN