Cp3bt26 – National CP3BT26 User Manual

Page 164

www.national.com

164

CP3BT26

Data bits are sensed by taking a majority vote of three sam-

ples latched near the midpoint of each baud (bit time). Nor-

mally, the position of the samples within the baud is

determined automatically, but software can override the au-

tomatic selection by setting the USMD bit in the UnMDSL2

register and programming the UnSPOS register.

Serial data input on the RXD pin is shifted into the RSFT

register. On receiving the complete character, the contents

of the RSFT register are copied into the UnRBUF register

and the Receive Buffer Full bit (URBF) is set. The URBF bit

is automatically cleared when software reads the character

from the URBUF register. The RSFT register is not software

accessible.

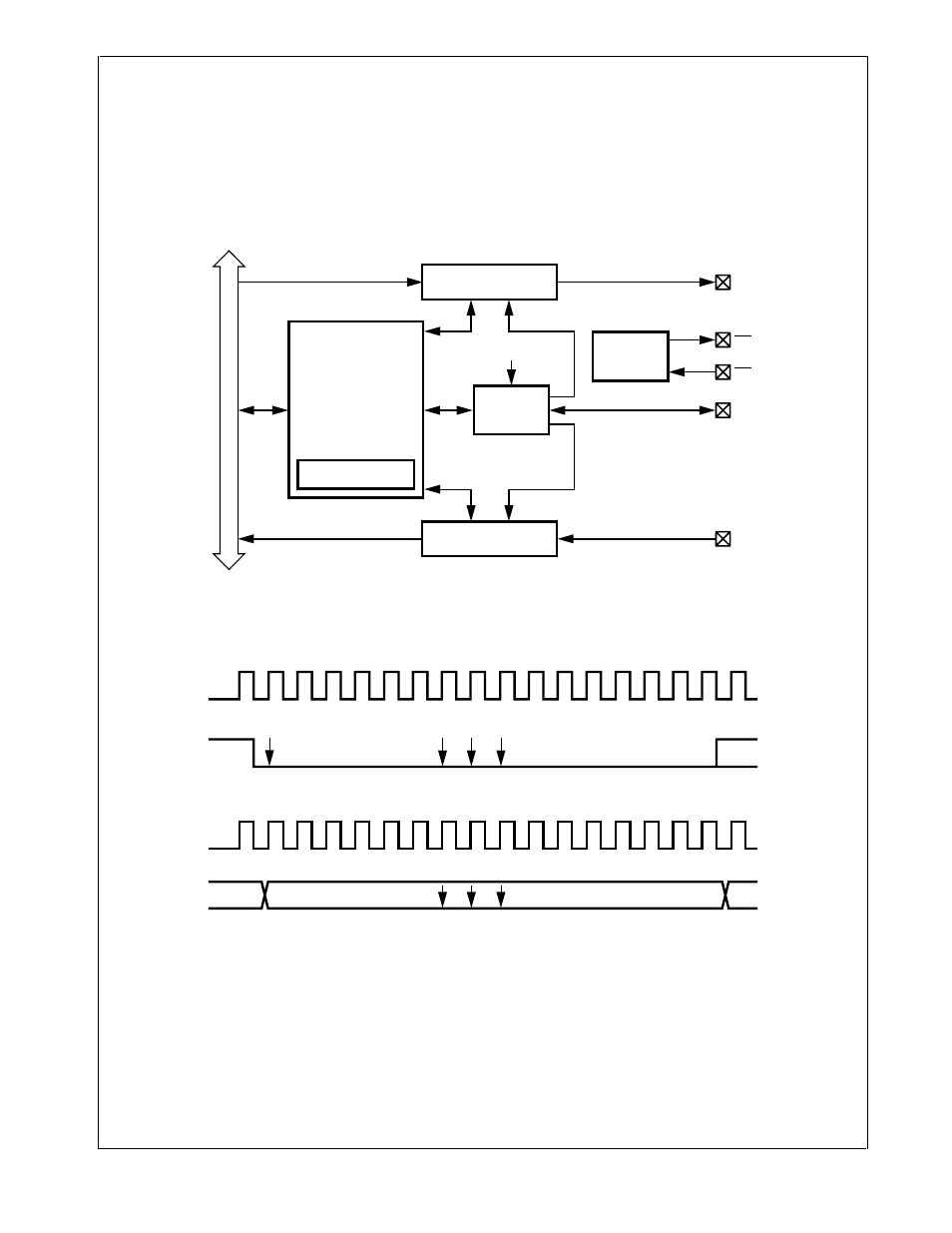

Figure 76.

UART Block Diagram

Figure 77.

UART Asynchronous Communication

TXD

Transmitter

Control and

Error Detection

Parity

Generator/Checker

RXD

Receiver

CKX

Baud Rate

Generator

Baud Clock

Baud Clock

System Clock

Inter

nal Bus

DS060

RTS

CTS

Flow Control

Logic

16

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

16

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

Sample

Sample

Sample

DATA (LSB)

STARTBIT

DATABIT

DS061