Cp3bt26 – National CP3BT26 User Manual

Page 44

www.national.com

44

CP3BT26

9.6.1

Device A Address Counter Register (ADCAn)

The Device A Address Counter register is a 32-bit, read/

write register. It holds the current 24-bit address of either the

source data item or the destination location, depending on

the state of the DIR bit in the CNTLn register. The ADA bit

of DMACNTLn register controls whether to adjust the point-

er in the ADCAn register by the step size specified in the

INCA field of DMACNTLn register. The upper 8 bits of the

ADCAn register are reserved and always clear.

9.6.2

Device A Address Register (ADRAn)

The Device A Address register is a 32-bit, read/write regis-

ter. It holds the 24-bit starting address of either the next

source data block, or the next destination data area, according

to the DIR bit in the DMACNTLn register. The upper 8 bits of

the ADRAn register are reserved and always clear.

9.6.3

Device B Address Counter Register (ADCBn)

The Device B Address Counter register is a 32-bit, read/

write register. It holds the current 24-bit address of either the

source data item, or the destination location, according to

the DIR bit in the CNTLn register. The ADCBn register is up-

dated after each transfer cycle by INCB field of the

DMACNTLn register according to ADB bit of the

DMACNTLn register. In direct (flyby) mode, this register is

not used.

The upper 8 bits of the ADCBn register are re-

served and always clear.

9.6.4

Device B Address Register (ADRBn)

The Device B Address register is a 32-bit, read/write regis-

ter. It holds the 24-bit starting address of either the next

source data block or the next destination data area, accord-

ing to the DIR bit in the CNTLn register. In direct (flyby)

mode, this register is not used.

The upper 8 bits of the AD-

CRBn register are reserved and always clear.

9.6.5

Block Length Counter Register (BLTCn)

The Block Length Counter register is a 16-bit, read/write

register. It holds the current number of DMA transfers to be

executed in the current block. BLTCn is decremented by one

after each transfer cycle. A DMA transfer may consist of 1 or

2 bytes, as selected by the DMACNTLn.TCS bit.

Note: 0000h is interpreted as 2

16

-1 transfer cycles.

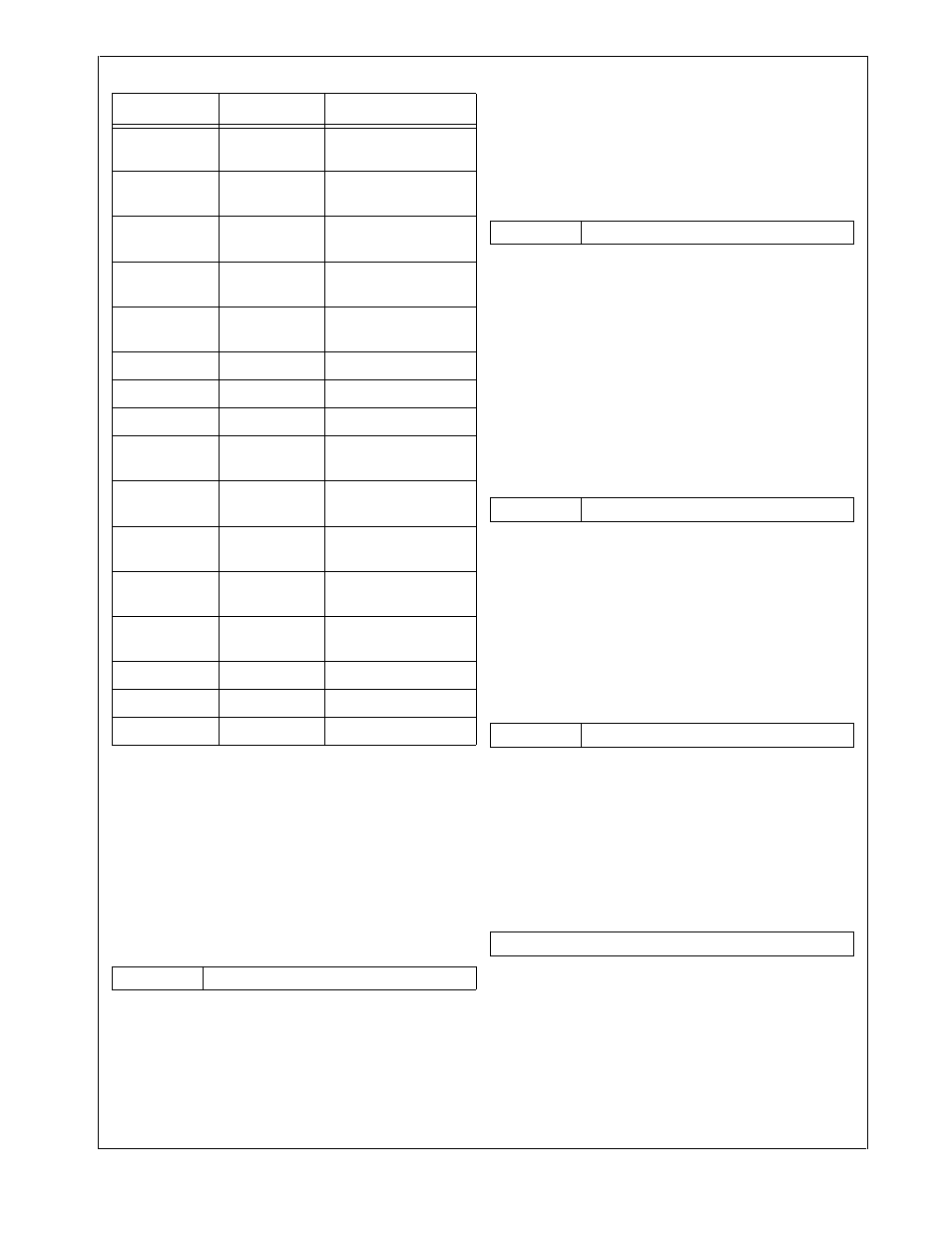

ADCA2

FF F840h

Device A Address

Counter Register

ADRA2

FF F844h

Device A Address

Register

ADCB2

FF F848h

Device B Address

Counter Register

ADRB2

FF F84Ch

Device B Address

Register

BLTC2

FF F850h

Block Length

Counter Register

BLTR2

FF F854h

Block Length Register

DMACNTL2

FF F85Ch

DMA Control Register

DMASTAT2

FF F85Eh

DMA Status Register

ADCA3

FF F860h

Device A Address

Counter Register

ADRA3

FF F864h

Device A Address

Register

ADCB3

FF F868h

Device B Address

Counter Register

ADRB3

FF F86Ch

Device B Address

Register

BLTC3

FF F870h

Block Length

Counter Register

BLTR3

FF F874h

Block Length Register

DMACNTL3

FF F87Ch

DMA Control Register

DMASTAT3

FF F87Eh

DMA Status Register

31

24

23

0

Reserved

Device A Address Counter

Table 18

DMA Controller Registers

Name

Address

Description

31

24

23

0

Reserved

Device A Address

31

24

23

0

Reserved

Device B Address Counter

31

24

23

0

Reserved

Device B Address

15

0

Block Length Counter