0 triple clock and reset, Triple clock and reset, Cp3 bt26 – National CP3BT26 User Manual

Page 51

51

www.national.com

CP3

BT26

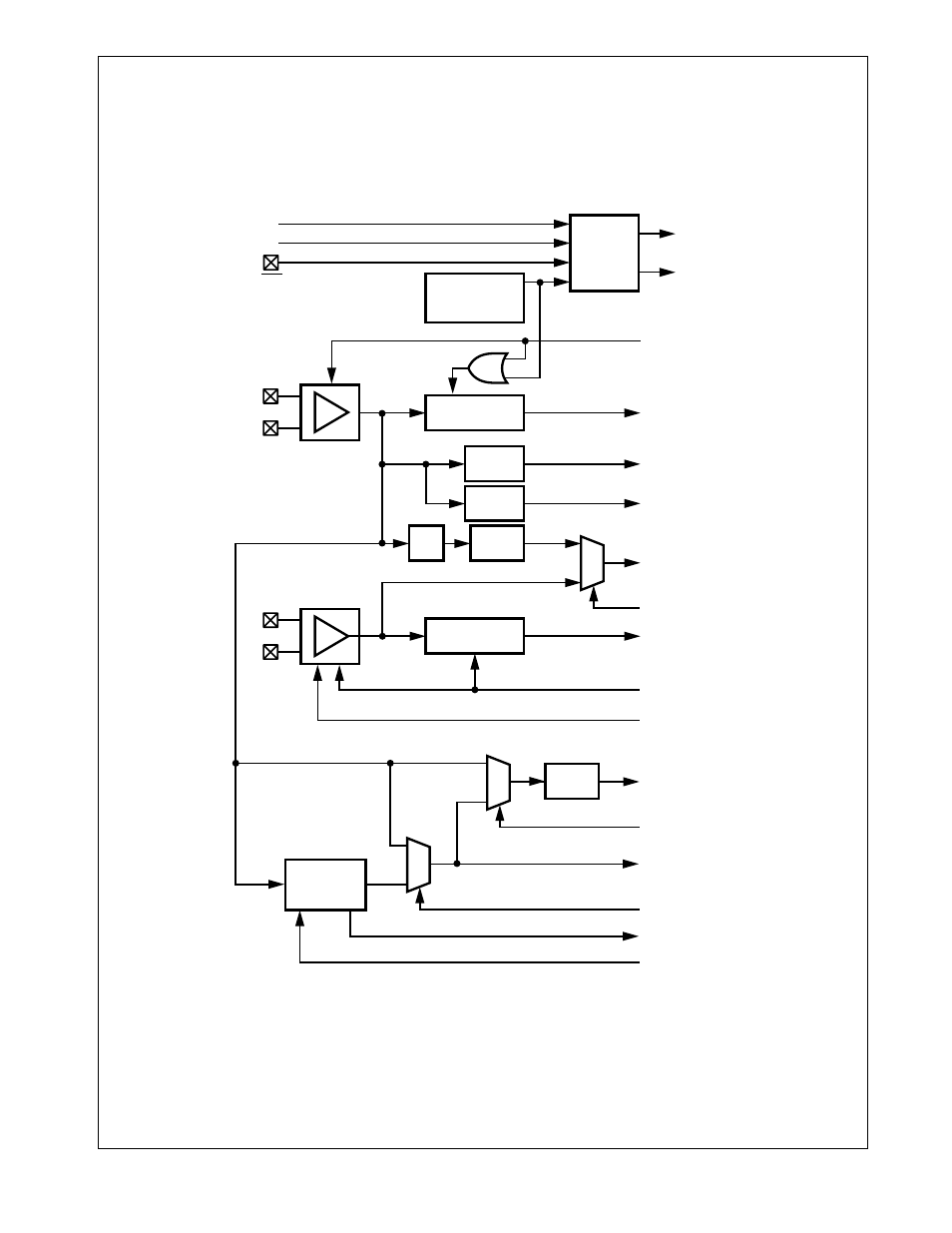

11.0 Triple Clock and Reset

The Triple Clock and Reset module generates a 12 MHz

Main Clock and a 32.768 kHz Slow Clock from external

crystal networks or external clock sources. It provides vari-

ous clock signals for the rest of the chip. It also provides the

main system reset signal, a power-on reset function, Main

Clock prescalers to generate two additional low-speed

clocks, and a 32-kHz oscillator start-up delay.

Figure 4 is block diagram of the Triple Clock and Reset mod-

ule.

Figure 4.

Triple Clock and Reset Module

Reset

Module

Device Reset

Stretched

Reset

Stop Main Osc

Good Main Clock

Power-On-Reset

Module (POR)

Start-Up-Delay

14-Bit Timer

TWM (Invalid Watchdog Service)

Flash Interface (Program/Erase Busy)

External Reset

Good Slow Clock

Start-Up-Delay

8-Bit Timer

Auxiliary Clock 1

4-Bit Aux1

Prescaler

Auxiliary Clock 2

4-Bit Aux2

Prescaler

Slow Clock

Slow Clock

Select

Main Clock

8-Bit

Prescaler

Mux

Slow Clock Prescaler

Preset

Time-out

System Clock

Fast Clock

Select

Mux

4-Bit

Prescaler

Fast Clock

Prescaler

PLL

(x3, x4, or x5)

Stop Slow Osc

Bypass

32 kHz Osc

Div.

by 2

Reset

Preset

Stop Main Osc.

High Frequency

Oscillator

X1CKI

X1CKO

Low Frequency

Oscillator

X2CKI

X2CKO

PLL Clock

Bypass PLL

Mux

Stop PLL

Stop PLL

Good PLL Clock

DS006