2 random number generator register set, Random number generator register set, Cp3 bt26 – National CP3BT26 User Manual

Page 89

89

www.national.com

CP3

BT26

17.2

RANDOM NUMBER GENERATOR

REGISTER SET

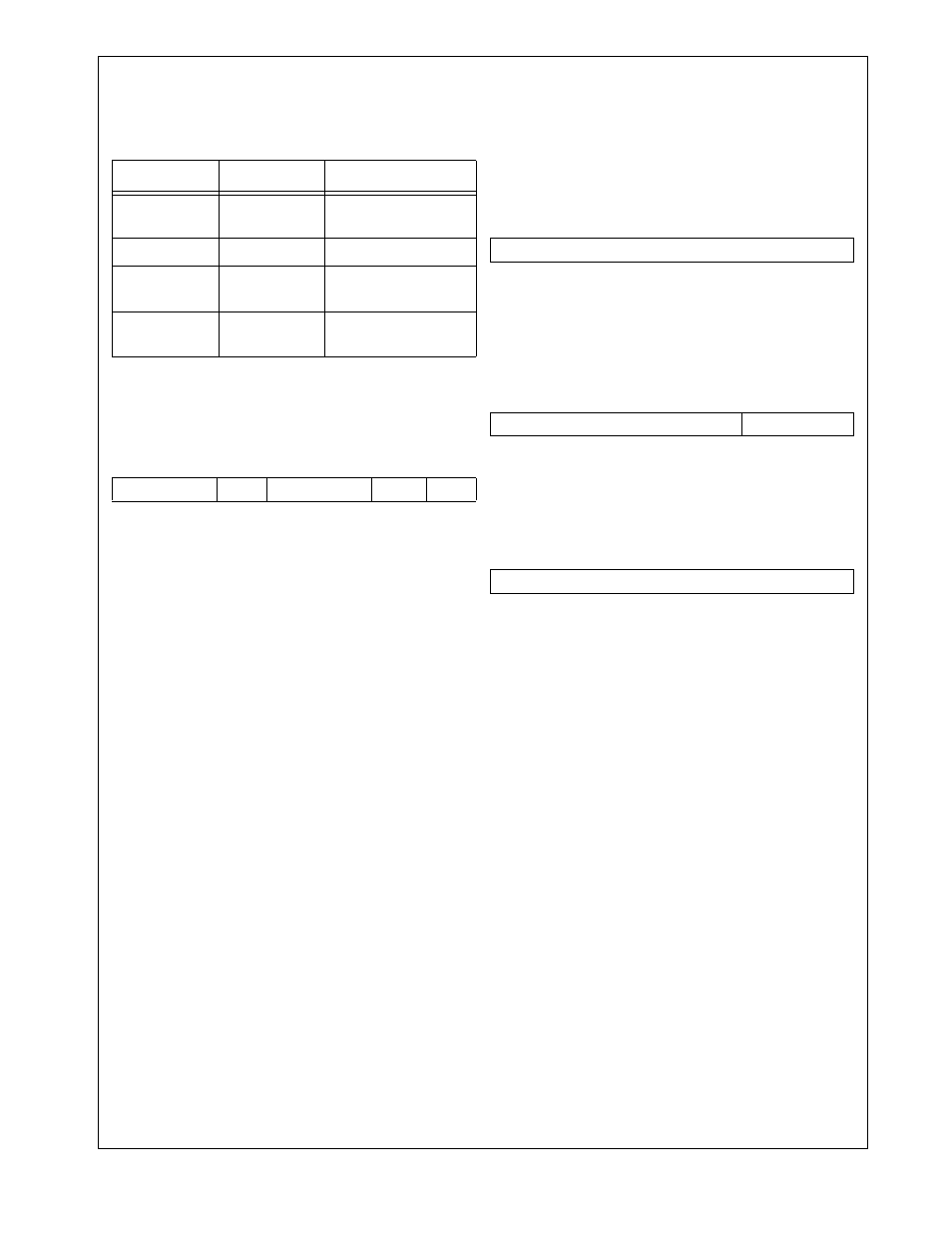

Table 34 lists the RNG registers.

17.2.1

RNG Control and Status Register (RNGCST)

The RNGCST register provides control and status bits for

the RNG module. This register is cleared at reset.

RNGE

The Random Number Generator Enable bit

enables the operation of the RNG. When this

bit is clear, the RNG module is disabled, and

both RNG oscillators are suspended.

0 – RNG module disabled.

1 – RNG module enabled.

DVALID

The Data Valid bit indicates whether valid

(random) data is available in the RNGD regis-

ter. This bit is cleared when the RNGD regis-

ter is read.

0 – RNGD register holds invalid data.

1 – RNGD register holds valid data.

IMASK

The Interrupt Mask bit controls whether an in-

terrupt request (IRQ3) will be asserted when

valid (random) data is available in the RNGD

register.

0 – RNG interrupt disabled.

1 – RNG interrupt enabled.

17.2.2

RNG Data Register (RNGD)

The RNGD register holds random data generated by the

RNG module. After reading the register, it is cleared and the

DVALID bit of the RNGCST register is cleared. When a new

word of valid (random) data becomes available in the RNGD

register, the DVALID bit is set and (if enabled) and interrupt

request is asserted.

17.2.3

RNG Divisor Register High (RNGDIVH)

This register holds the two most significant bits of the

RNGDIV clock divisor. See the description of the RNGDIVL

register.

17.2.4

RNG Divisor Register Low (RNGDIVL)

This register holds the 16 least significant bits the RNGDIV

clock divisor.

The RNGDIV clock divisor is used to generate the sampling

strobe for loading random bits into the shift register. The di-

visor is applied to the System Clock source. The maximum

frequency after division is 800 Hz. For example, a System

Clock frequency of 24 MHz would require an RNGDIV value

of 30,000 (7530h) or greater. The default RNGDIV value is

0000 83D6h.

Table 37

RNG Registers

Name

Address

Description

RNGCST

FF F280h

RNG Control and

Status Register

RNGD

FF F282h

RNG Data Register

RNGDIVH

FF F284h

RNG Divisor Register

High

RNGDIVL

FF F286h

RNG Divisor Register

Low

15

6

5

4

2

1

0

Reserved

IMSK

Reserved

DVALID RNGE

15

0

RNGD15:0

15

2

1

0

Reserved

RNGDIV17:16

15

0

RNGDIV15:0