6 stacks, 7 instruction set, Stacks – National CP3BT26 User Manual

Page 19: Instruction set, Cp3 bt26

19

www.national.com

CP3

BT26

5.6

STACKS

A stack is a last-in, first-out data structure for dynamic stor-

age of data and addresses. A stack consists of a block of

memory used to hold the data and a pointer to the top of the

stack. As more data is pushed onto a stack, the stack grows

downward in memory. The CR16C supports two types of

stacks: the interrupt stack and program stacks.

5.6.1

Interrupt Stack

The processor uses the interrupt stack to save and restore

the program state during the exception handling. Hardware

automatically pushes this data onto the interrupt stack be-

fore entering an exception handler. When the exception

handler returns, hardware restores the processor state with

data popped from the interrupt stack. The interrupt stack

pointer is held in the ISP register.

5.6.2

Program Stack

The program stack is normally used by software to save and

restore register values on subroutine entry and exit, hold lo-

cal and temporary variables, and hold parameters passed

between the calling routine and the subroutine. The only

hardware mechanisms which operate on the program stack

are the PUSH, POP, and POPRET instructions.

5.6.3

User and Supervisor Stack Pointers

To support multitasking operating systems, support is pro-

vided for two program stack pointers: a user stack pointer

and a supervisor stack pointer. When the PSR.U bit is clear,

the SP register is used for all program stack operations. This

is the default mode when the user/supervisor protection

mechanism is not used, and it is the supervisor mode when

protection is used.

When the PSR.U bit is set, the processor is in user mode,

and the USP register is used as the program stack pointer.

User mode can only be entered using the JUSR instruction,

which performs a jump and sets the PSR.U bit. User mode

is exited when an exception is taken and re-entered when

the exception handler returns. In user mode, the LPRD in-

struction cannot be used to change the state of processor

registers (such as the PSR).

5.7

INSTRUCTION SET

Table 4 lists the operand specifiers for the instruction set,

and Table 5 is a summary of all instructions. For each in-

struction, the table shows the mnemonic and a brief de-

scription of the operation performed.

In the mnemonic column, the lower-case letter “i” is used to

indicate the type of integer that the instruction operates on,

either “B” for byte or “W” for word. For example, the notation

ADDi for the “add” instruction means that there are two

forms of this instruction, ADDB and ADDW, which operate

on bytes and words, respectively.

Similarly, the lower-case string “cond” is used to indicate the

type of condition tested by the instruction. For example, the

notation Jcond represents a class of conditional jump in-

structions: JEQ for Jump on Equal, JNE for Jump on Not

Equal, etc. For detailed information on all instructions, see

the CompactRISC CR16C Programmer's Reference Manu-

al.

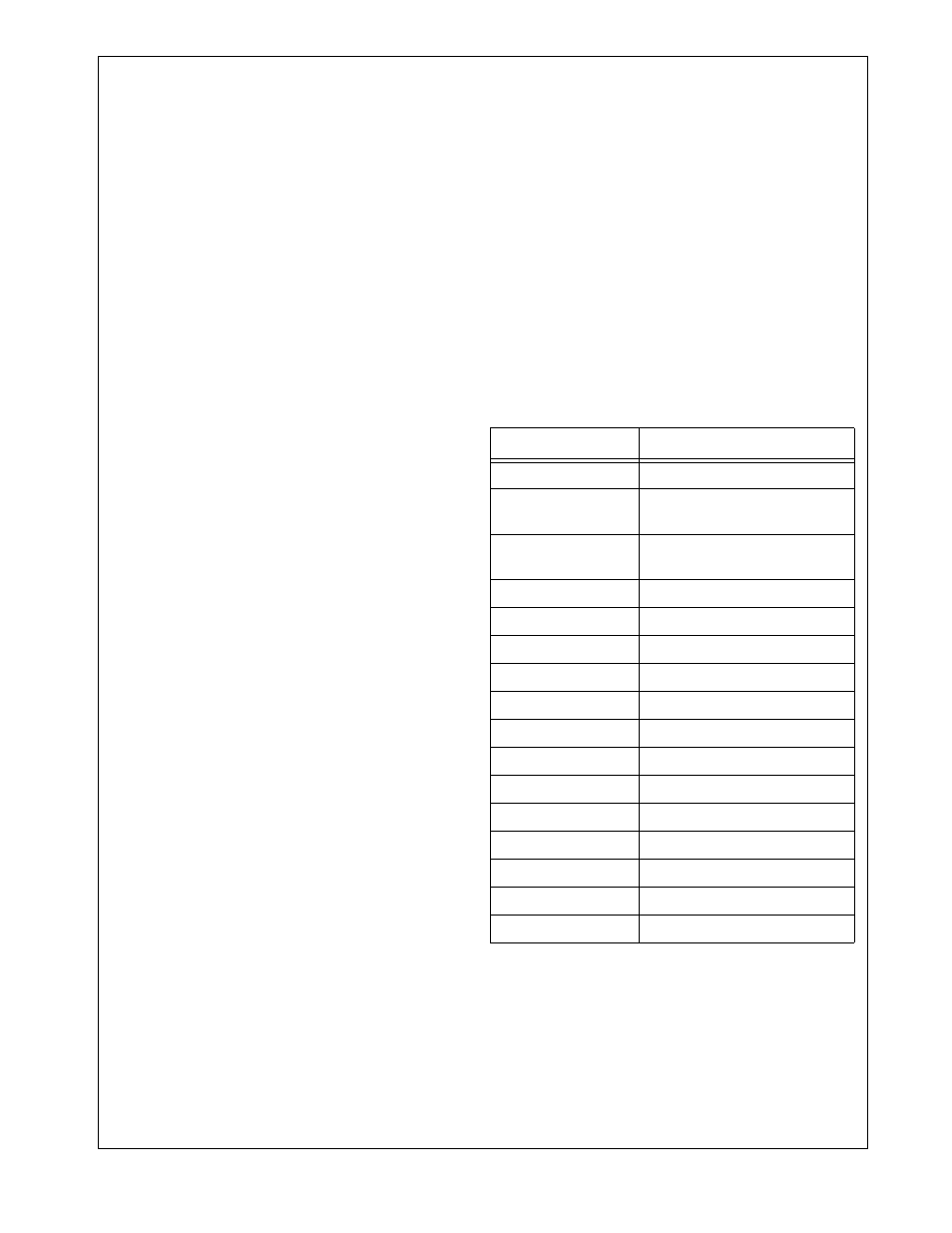

Table 4

Key to Operand Specifiers

Operand Specifier

Description

abs

Absolute address

disp

Displacement (numeric suffix

indicates number of bits)

imm

Immediate operand (numeric suf-

fix indicates number of bits)

Iposition

Bit position in memory

Rbase

Base register (relative mode)

Rdest

Destination register

Rindex

Index register

RPbase, RPbasex

Base register pair (relative mode)

RPdest

Destination register pair

RPlink

Link register pair

Rposition

Bit position in register

Rproc

16-bit processor register

Rprocd

32-bit processor register

RPsrc

Source register pair

RPtarget

Target register pair

Rsrc, Rsrc1, Rsrc2

Source register