Cp3bt26 – National CP3BT26 User Manual

Page 92

www.national.com

92

CP3BT26

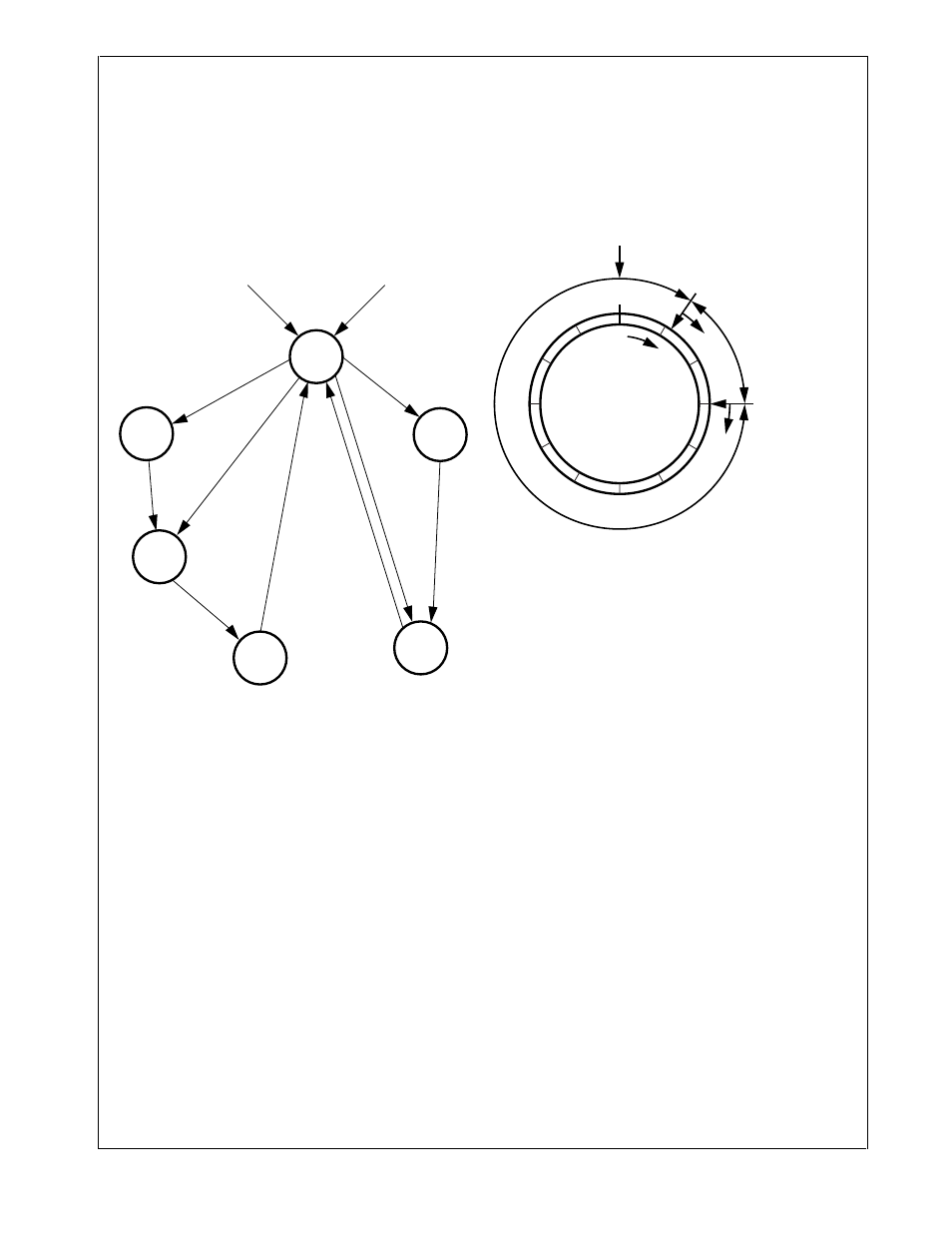

Bidirectional Control Endpoint FIFO0 Operation

FIFO0 should be used for the bidirectional control endpoint

0. It can be configured to receive data sent to the default ad-

dress with the DEF bit in the EPC0 register. Isochronous

transfers are not supported for the control endpoint.

The Endpoint 0 FIFO can hold a single receive or transmit

packet with up to 8 bytes of data. Figure 30 shows the basic

operation in both receive and transmit direction.

Note: The actual current operating state is not directly vis-

ible to software.

Figure 30.

Endpoint 0 Operation

A packet written to the FIFO is transmitted if an IN token for

the respective endpoint is received. If an error condition is

detected, the packet data remains in the FIFO and transmis-

sion is retried with the next IN token.

The FIFO contents can be flushed to allow response to an

OUT token or to write new data into the FIFO for the next IN

token.

If an OUT token is received for the FIFO, software is in-

formed that the FIFO has received data only if there was no

error condition (CRC or STUFF error). Erroneous recep-

tions are automatically discarded.

Transmit Endpoint FIFO Operation (TXFIFO1, TXFIFO2,

TXFIFO3)

The Transmit FIFOs for endpoints 1, 3, and 5 support bulk,

interrupt, and isochronous USB packet transfers larger than

the actual FIFO size. Therefore, software must update the

FIFO contents while the USB packet is transmitted on the

bus. Figure 31 illustrates the operation of the transmit

FIFOs.

Figure 31.

Transmit FIFO Operation

TFnS

The Transmit FIFO n Size is the total number

of bytes available within the FIFO.

TXRP

The Transmit Read Pointer is incremented ev-

ery time the Endpoint Controller reads from

the transmit FIFO. This pointer wraps around

to zero if TFnS is reached. TXRP is never in-

cremented beyond the value of the write

pointer TXWP. An underrun condition occurs if

TXRP equals TXWP and an attempt is made

to transmit more bytes when the LAST bit in

the TXCMDx register is not set.

TXWP

The Transmit Write Pointer is incremented ev-

ery time software writes to the transmit FIFO.

This pointer wraps around to zero if TFnS is

reached. If an attempt is made to write more

bytes to the FIFO than actual space available

(FIFO overrun), the write to the FIFO is ig-

nored. If so, TCOUNT is checked for an indi-

cation of the number of empty bytes

remaining.

TXFL

The Transmit FIFO Level indicates how many

bytes are currently in the FIFO. A FIFO warn-

ing is issued if TXFL decreases to a specific

value. The respective WARNn bit in the FWR

register is set if TXFL is equal to or less than

the number specified by the TFWL bit in the

TXCn register.

TCOUNT

The Transmit FIFO Count indicates how many

empty bytes can be filled within the transmit

FIFO. This value is accessible by software in

the TXSn register.

FLUSH Bit, TXC0 Register

FLUSH Bit, RXC0 Register

RX_EN Bit,

RXC0 Register

OUT or

SETUP

Token

SETUP

Token

FIFO0 Empty

(All Data Read)

Transmission

Done

IN Token

TX_EN Bit,

TXC0

Register

Write to TXD0

IDLE

RXWAIT

RX

TX

TXWAIT

TXFILL

TX_EN Bit,

TXC0 Register

(Zero-Length

Packet)

DS050

FLUSH (Resets TXRP and TXWP)

TXRP

TXFL = TXWP

-

TXRP

TXWP

TCOUNT = TXRP

-

TXWP (= TFnS

-

TXFL)

TX FIFO n

0X0

TFnS

-

1

+

+

+

DS051