3 bit clock generation, 4 frame clock generation, 5 audio interface operation – National CP3BT26 User Manual

Page 146: Bit clock generation, Frame clock generation, Audio interface operation, Cp3bt26

www.national.com

146

CP3BT26

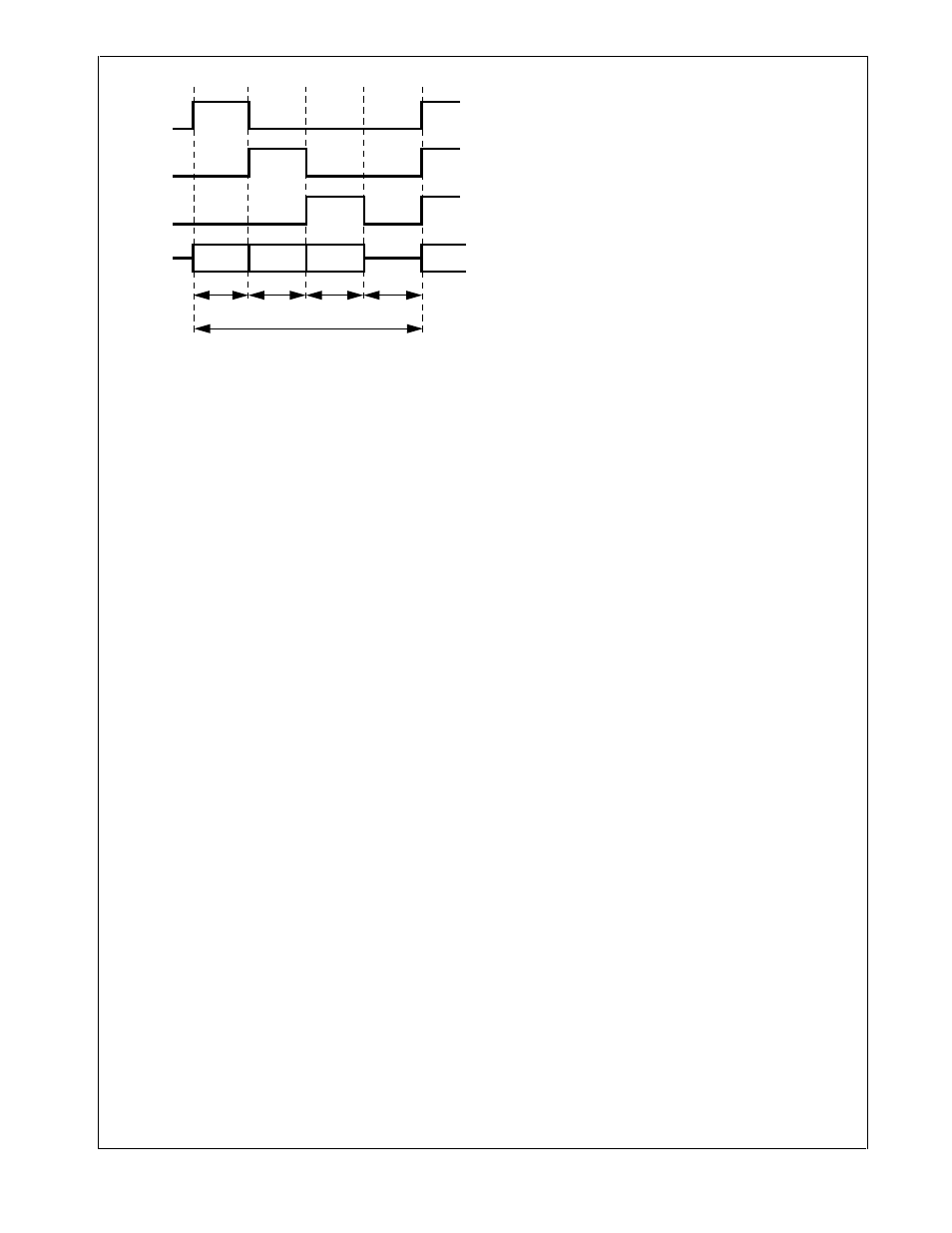

Figure 69.

Accessing Three Devices in Network Mode

20.3

BIT CLOCK GENERATION

An 8-bit prescaler is provided to divide the audio interface

input clock down to the required bit clock rate. Software can

choose between two input clock sources, a primary and a

secondary clock source.

On the CP3BT26, the two optional input clock sources are

the 12-MHz Aux1 clock (also used for the Bluetooth LLC)

and the 48-MHz PLL output clock (also used by the USB

node). The input clock is divided by the value of the prescal-

er BCPRS[7:0] + 1 to generate the bit clock.

The bit clock rate f

bit

can be calculated by the following

equation:

f

bit

= n × f

Sample

× Data Length

n = Number of Slots per Frame

f

Sample

= Sample Frequency in Hz

Data Length = Length of data word in multiples of 8 bits

The ideal required prescaler value P

ideal

can be calculated

as follows:

P

ideal

= f

Audio In

/ f

bit

The real prescaler must be set to an integer value, which

should be as close as possible to the ideal prescaler value,

to minimize the bit clock error, f

bit_error

.

f

bit_error

[%] = (f

bit

- f

Audio In

/P

real

) / f

bit

× 100

Example:

The audio interface is used to transfer 13-bit linear PCM

data for one audio channel at a sample rate of 8k samples

per second. The input clock of the audio interface is 12 MHz.

Furthermore, the codec requires a minimum bit clock of 256

kHz to operate properly. Therefore, the number of slots per

frame must be set to 2 (network mode) although actually

only one slot (slot 0) is used. The codec and the audio inter-

face will put their data transmit pins in TRI-STATE mode af-

ter the PCM data word has been transferred. The required

bit clock rate f

bit

can be calculated by the following equation:

f

bit

= n × f

Sample

× Data Length = 2 × 8 kHz × 16 = 256 kHz

The ideal required prescaler value P

ideal

can be calculated

as follows:

P

ideal

= f

Audio In

/ f

bit

= 12 MHz / 256 kHz = 46.875

Therefore, the real prescaler value is 47. This results in a bit

clock error equal to:

f

bit_error

= (f

bit

- f

Audio In

/P

real

) / f

bit

× 100

= (256 kHz - 12 MHz/47) / 256 kHz × 100 = 0.27%

20.4

FRAME CLOCK GENERATION

The clock for the frame synchronization signals is derived

from the bit clock of the audio interface. A 7-bit prescaler is

used to divide the bit clock to generate the frame sync clock

for the receive and transmit operations. The bit clock is di-

vided by FCPRS + 1. In other words, the value software

must write into the ACCR.FCPRS field is equal to the bit

number per frame minus one. The frame may be longer than

the valid data word but it must be equal to or larger than the

8- or 16-bit word. Even if 13-, 14-, or 15-bit data is being

used, the frame width must always be at least 16 bits wide.

In addition, software can specify the length of a long frame

sync signal. A long frame sync signal can be either 6, 13,

14, 15, or 16 bits long, depending on the external codec be-

ing used. The frame sync length can be configured by the

Frame Sync Length field (FSL) in the AGCR register.

20.5

AUDIO INTERFACE OPERATION

20.5.1

Clock Configuration

The Aux1 clock (generated by the Clock module described

in Section 11.9) must be configured, because it is the time

base for the AAI module. Software must write an appropri-

ate divisor to the ACDIV1 field of the PRSAC register to pro-

vide a 12 MHz input clock. Software also must enable the

Aux1 clock by setting the ACE1 bit in the CRCTRL register.

For example:

PRSAC &= 0xF0;

// Set Aux1 prescaler to 1 (F = 12 MHz)

CRCTRL |= ACE1; // Enable Aux1 clk

20.5.2

Interrupts

The interrupt logic of the AAI combines up to four interrupt

sources and generates one interrupt request signal to the

Interrupt Control Unit (ICU).

The four interrupt sources are:

RX FIFO Overrun - ASCR.RXEIP = 1

RX FIFO Almost Full (Warning Level) - ASCR.RXIP = 1

TX FIFO Under run - ASCR.TXEIP = 1

TX FIFO Almost Empty (Warning Level) - ASCR.TXIP=1

In addition to the dedicated input to the ICU for handling

these interrupt sources, the Serial Frame Sync (SFS) signal

is an input to the MIWU (see Section 13.0), which can be

programmed to generate edge-triggered interrupts.

Slot1

Frame

Slot0

SFS

SRCLK

(auxiliary

frame sync)

SRFS

(auxiliary

frame sync)

STD/SRD

Data from/to

Codec 1

Data from/to

Codec 3

Data from/to

Codec 2

Slot2

Slot2

DS057