Cp3 bt26 – National CP3BT26 User Manual

Page 201

201

www.national.com

CP3

BT26

26.2.4

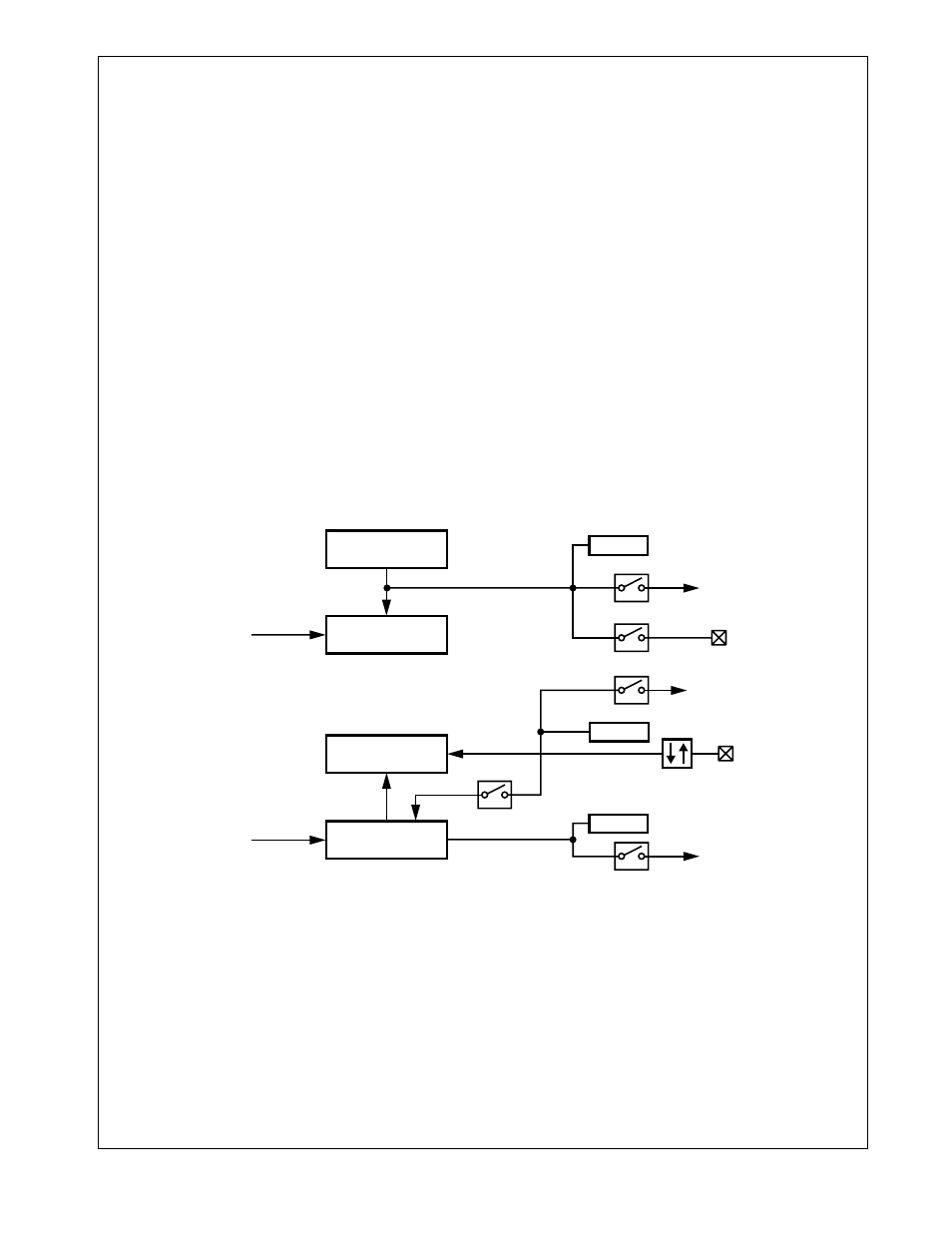

Mode 4: Input Capture Plus Timer

Mode 4 is the Single Input Capture and Single Timer mode,

which provides one external event counter and one system

timer.

Figure 103 is a block diagram of the Multi-Function Timer

configured to operate in Mode 4. This mode offers a combi-

nation of Mode 3 and Mode 2 functions. Timer/Counter 1 is

used as a system timer as in Mode 3 and Timer/Counter 2

is used as a capture timer as in Mode 2, but with a single

input rather than two inputs.

Timer/Counter 1 (TCNT1) operates the same as in Mode 3.

It counts down at the rate of the selected clock. On under-

flow, it is reloaded from the TCRA register and counting pro-

ceeds down from the reloaded value. The TA pin is toggled

on each underflow, when this function is enabled by the

TAEN bit. When the TA pin is toggled from low to high, it sets

the TCPND interrupt pending bit and also generates an in-

terrupt if the interrupt is enabled by the TAIEN bit. A 50%

duty cycle PWM signal can be generated on TA without any

further action from the CPU.

Timer/Counter 2 (TCNT1) counts down at the rate of the se-

lected clock. The TB pin functions as the capture input. A

transition received on TB transfers the timer contents to the

TCRB register. The input pin can be configured to sense ei-

ther rising or falling edges.

The TB input can be configured to preset the counter to

FFFFh on reception of a valid capture event. In this case,

the current value of the counter is transferred to the capture

register and then the counter is preset to FFFFh.

The values captured in the TCRB register at different times

reflect the elapsed time between transitions on the TA pin.

The input signal on TB must have a pulse width equal to or

greater than one System Clock cycle.

There are two separate interrupts associated with the cap-

ture timer, each with its own enable bit and pending bit. The

two interrupt events are reception of a transition on TB and

underflow of the TCNT2 counter. The enable bits for these

events are TBIEN and TDIEN, respectively.

Neither Timer/Counter 1 (TCNT1) nor Timer/Counter 2

(TCNT2) can be configured to operate as an external event

counter or to operate in the pulse-accumulate mode be-

cause the TB input is used as a capture input. Attempting to

select one of these configurations will cause one or both

counters to stop. In this mode, Timer/Counter 2 must be en-

abled at all times.

Figure 103.

Input Capture Plus Timer Mode

Timer/Counter 1

TCNT1

Timer 1

Clock

Reload A

TCRA

TAPND

TAIEN

Timer

Interrupt 1

TAEN

TA

Underflow

TDPND

TDIEN

Timer

Interrupt 2

Timer/Counter 2

TnCNT2

Timer 2

Clock

Capture B

TCRB

TB

TBPND

TBIEN

Timer

Interrupt 1

Preset

TBEN

DS087