Cp3 bt26 – National CP3BT26 User Manual

Page 207

207

www.national.com

CP3

BT26

27.1.1

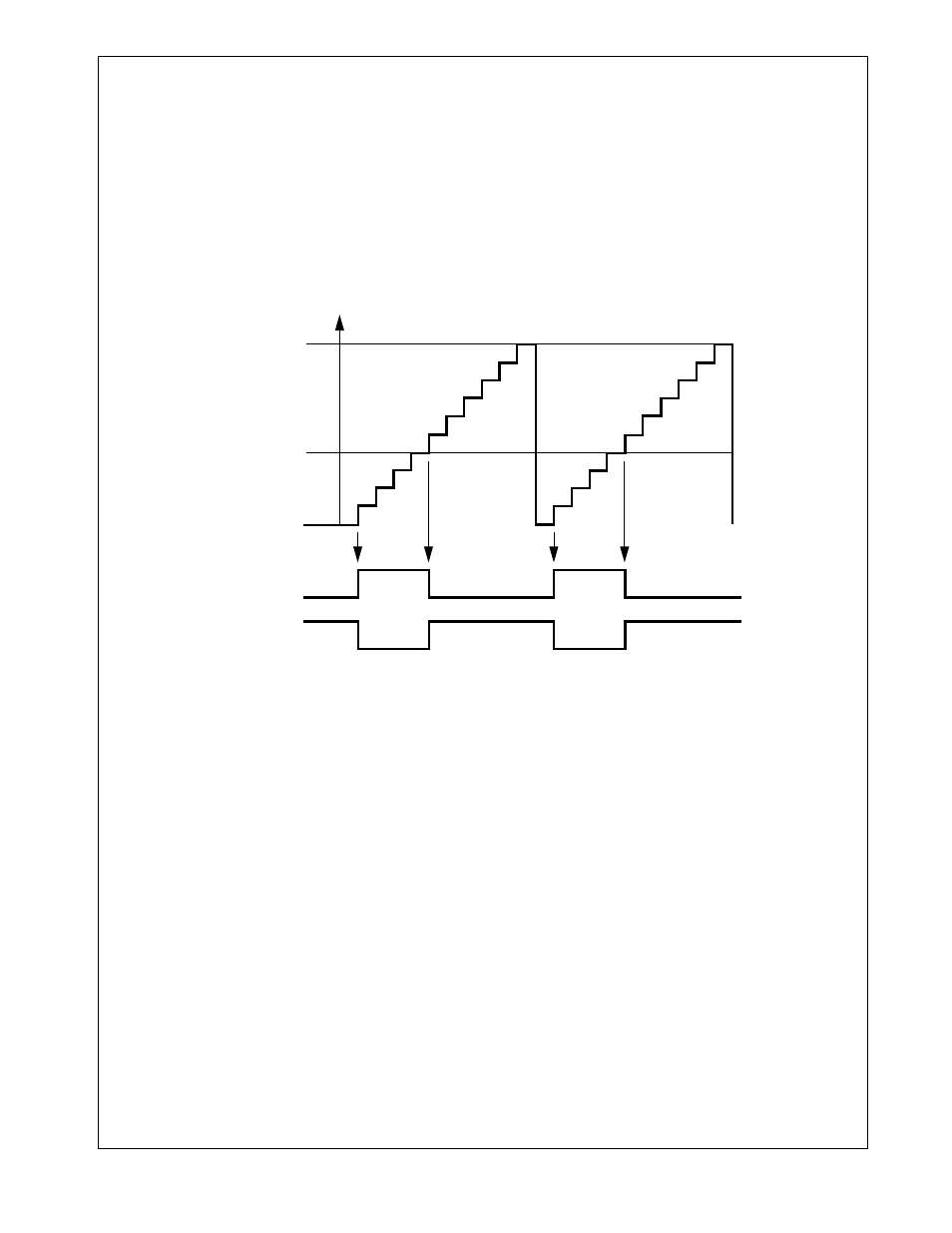

Dual 8-bit PWM Mode

Each timer subsystem may be configured to generate two

fully independent PWM waveforms on the respective TIOx

pins. In this mode, the counter COUNTx is split and oper-

ates as two independent 8-bit counters. Each counter incre-

ments at the rate determined by the clock prescaler.

Each of the two 8-bit counters may be started and stopped

separately using the corresponding TxRUN bits. Once ei-

ther of the two 8-bit timers is running, the clock prescaler

starts counting. Once the clock prescaler counter value

matches the value of the associated CxPRSC register field,

COUNTx is incremented.

The period of the PWM output waveform is determined by

the value of the PERCAPx register. The TIOx output starts

at the default value as programmed in the IOxCTL.PxPOL

bit. Once the counter value reaches the value of the period

register PERCAPx, the counter is cleared on the next

counter increment. On the following increment from 00h to

01h, the TIOx output will change to the opposite of the de-

fault value.

The duty cycle of the PWM output waveform is controlled by

the DTYCAPx register value. Once the counter value reach-

es the value of the duty cycle register DTYCAPx, the PWM

output TIOx changes back to its default value on the next

counter increment. Figure 105 illustrates this concept.

Figure 105.

VTU PWM Generation

The period time is determined by the following formula:

PWM Period = (PERCAPx + 1) × (CxPRSC + 1) × T

CLK

The duty cycle in percent is calculated as follows:

Duty Cycle = (DTYCAPx / (PERCAPx + 1)) × 100

If the duty cycle register (DTYCAPx) holds a value which is

greater than the value held in the period register (PER-

CAPx) the TIOx output will remain at the opposite of its de-

fault value which corresponds to a duty cycle of 100%. If the

duty cycle register (DTYCAPx) register holds a value of 00h,

the TIOx output will remain at the default value which corre-

sponds to a duty cycle of 0%, in which case the value in the

PERCAPx register is irrelevant. This scheme allows the

duty cycle to be programmed in a range from 0% to 100%.

In order to allow fully synchronized updates of the period

and duty cycle compare values, the PERCAPx and DTY-

CAPx registers are double buffered when operating in PWM

mode. Therefore, if software writes to either the period or

duty cycle register while either of the two PWM channels is

enabled, the new value will not take effect until the counter

value matches the previous period value or the timer is

stopped.

Reading the PERCAPx or DTYCAPx register will always re-

turn the most recent value written to it.

The counter registers can be written if both 8-bit counters

are stopped. This allows software to preset the counters be-

fore starting, which can be used to generate PWM output

waveforms with a phase shift relative to each other. If the

counter is written with a value other than 00h, it will start in-

crementing from that value. The TIOx output will remain at

its default value until the first 00h to 01h transition of the

counter value occurs. If the counter is preset to values which

are less than or equal to the value held in the period register

(PERCAPx) the counter will count up until a match between

the counter value and the PERCAPx register value occurs.

The counter will then be cleared and continue counting up.

Alternatively, the counter may be written with a value which

is greater than the value held in the period register. In that

case the counter will count up to FFh, then roll over to 00h.

In any case, the TIOx pin always changes its state at the

00h to 01h transition of the counter.

Software may only write to the COUNTx register if both

TxRUN bits of a timer subsystem are clear. Any writes to the

counter register while either timer is running will be ignored.

TIOx (PxPOL = 0)

DTYCAPx

TxRUN = 1

COUNTx

00

01

02

03

04

05

06

07

08

09

0A

00

01

02

03

04

05

06

07

08

09

0A

TIOx (PxPOL = 1)

PERCAPx

DS089