3 processor status register (psr), Processor status register (psr), Cp3bt26 – National CP3BT26 User Manual

Page 16

www.national.com

16

CP3BT26

5.2.4

Interrupt Base Register (INTBASE)

The INTBASE register holds the address of the dispatch ta-

ble for exceptions. The dispatch table can be located any-

where in the CPU address space. When loading the

INTBASE register, bits 31 to 24 and bit 0 must written with 0.

5.3

PROCESSOR STATUS REGISTER (PSR)

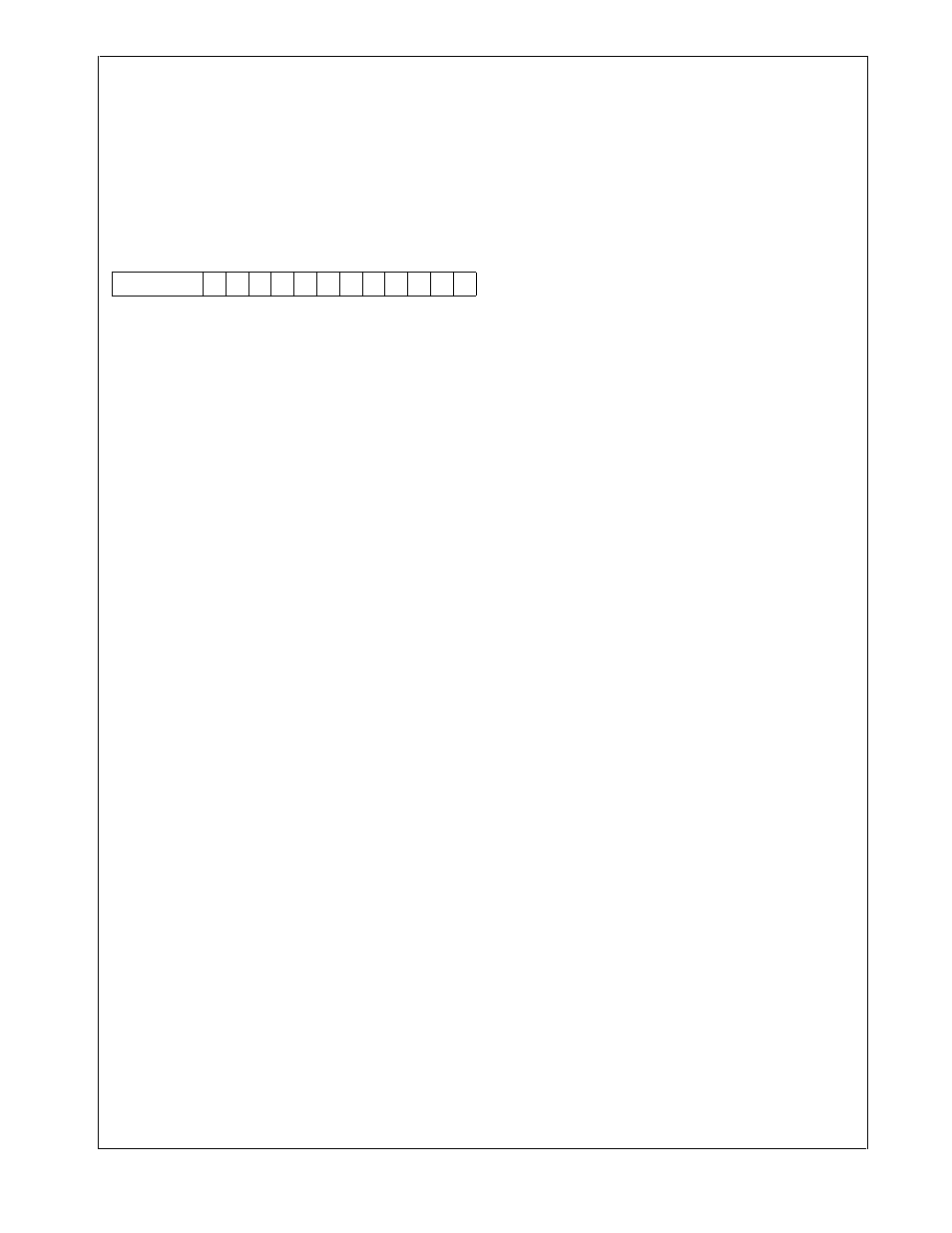

The PSR provides state information and controls operating

modes for the CPU. The format of the PSR is shown below.

C

The Carry bit indicates whether a carry or bor-

row occurred after addition or subtraction.

0

–

No carry or borrow occurred.

1

–

Carry or borrow occurred.

T

The Trace bit enables execution tracing, in

which a Trace trap (TRC) is taken after every

instruction. Tracing is automatically disabled

during the execution of an exception handler.

0

–

Tracing disabled.

1

–

Tracing enabled.

L

The Low bit indicates the result of the last

comparison operation, with the operands in-

terpreted as unsigned integers.

0

–

Second operand greater than or equal to

first operand.

1

–

Second operand less than first operand.

U

The User Mode bit controls whether the CPU

is in user or supervisor mode. In supervisor

mode, the SP register is used for stack opera-

tions. In user mode, the USP register is used

instead. User mode is entered by executing

the Jump USR instruction. When an exception

is taken, the exception handler automatically

begins execution in supervisor mode. The

USP register is accessible using the Load

Processor Register (LPR/LPRD) instruction in

supervisor mode. In user mode, an attempt to

access the USP register generates a UND

trap.

0

–

CPU is executing in supervisor mode.

1

–

CPU is executing in user mode.

F

The Flag bit is a general condition flag for sig-

nalling exception conditions or distinguishing

the results of an instruction, among other

thing uses. For example, integer arithmetic in-

structions use the F bit to indicate an overflow

condition after an addition or subtraction oper-

ation.

Z

The Zero bit is used by comparison opera-

tions. In a comparison of integers, the Z bit is

set if the two operands are equal. If the oper-

ands are unequal, the Z bit is cleared.

0

–

Source and destination operands un-

equal.

1

–

Source and destination operands equal.

N

The Negative bit indicates the result of the last

comparison operation, with the operands in-

terpreted as signed integers.

0

–

Second operand greater than or equal to

first operand.

1

–

Second operand less than first operand.

E

The Local Maskable Interrupt Enable bit en-

ables or disables maskable interrupts. If this

bit and the Global Maskable Interrupt Enable

(I) bit are both set, all interrupts are enabled.

If either of these bits is clear, only the non-

maskable interrupt is enabled. The E bit is set

by the Enable Interrupts (EI) instruction and

cleared by the Disable Interrupts (DI) instruc-

tion.

0

–

Maskable interrupts disabled.

1

–

Maskable interrupts enabled.

P

The Trace Trap Pending bit is used together

with the Trace (T) bit to prevent a Trace (TRC)

trap from occurring more than once for one in-

struction. At the beginning of the execution of

an instruction, the state of the T bit is copied

into the P bit. If the P bit remains set at the end

of the instruction execution, the TRC trap is

taken.

0

–

No trace trap pending.

1

–

Trace trap pending.

I

The Global Maskable Interrupt Enable bit is

used to enable or disable maskable interrupts.

If this bit and the Local Maskable Interrupt En-

able (E) bit are both set, all maskable inter-

rupts are taken. If either bit is clear, only the

non-maskable interrupt is taken. Unlike the E

bit, the I bit is automatically cleared when an

interrupt occurs and automatically set upon

completion of an interrupt handler.

0

–

Maskable interrupts disabled.

1

–

Maskable interrupts enabled.

Bits Z, C, L, N, and F of the PSR are referenced from as-

sembly language by the condition code in conditional

branch instructions. A conditional branch instruction may

cause a branch in program execution, based on the value of

one or more of these PSR bits. For example, one of the

Bcond instructions, BEQ (Branch EQual), causes a branch

if the PSR.Z bit is set.

On reset, bits 0 through 11 of the PSR are cleared, except

for the PSR.E bit, which is set. On warm reset, the values of

each bit before reset are copied into the R2 general-pur-

pose register. Bits 4 and 8 of the PSR have a constant value

of 0. Bits 12 through 15 are reserved. In general, status bits

are modified only by specific instructions. Otherwise, status

bits maintain their values throughout instructions which do

not implicitly affect them.

15

12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

I

P

E

0

N

Z

F

0

U

L

T

C