Cp3bt26 – National CP3BT26 User Manual

Page 198

www.national.com

198

CP3BT26

26.2.1

Mode 1: Processor-Independent PWM

Mode 1 is the Processor-Independent Pulse Width Modula-

tion (PWM) mode, which generates pulses of a specified

width and duty cycle, and which also provides a separate

general-purpose timer/counter.

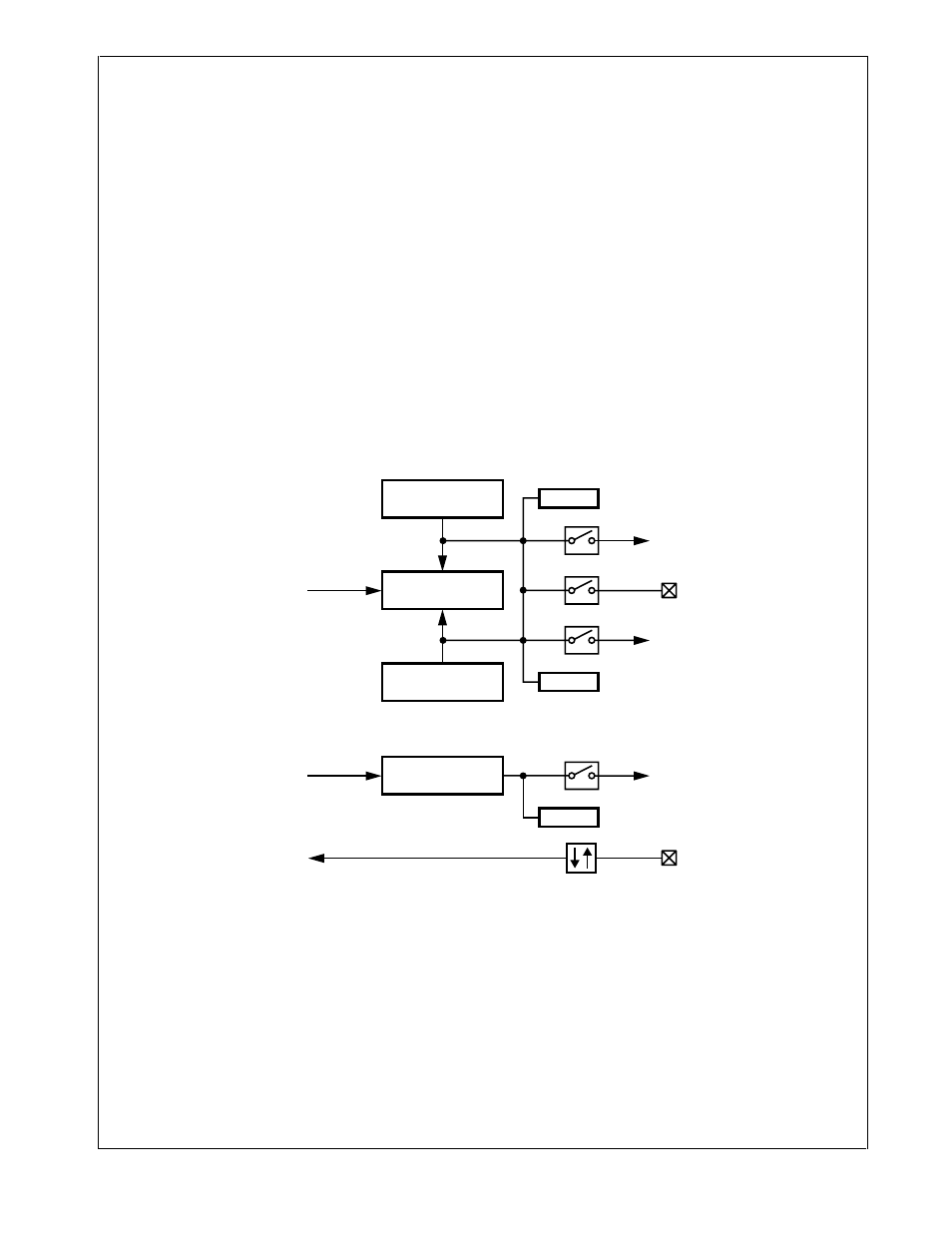

Figure 100 is a block diagram of the Multi-Function Timer

configured to operate in Mode 1. Timer/Counter 1 (TCNT1)

functions as the time base for the PWM timer. It counts

down at the clock rate selected for the counter. When an un-

derflow occurs, the timer register is reloaded alternately

from the TCRA and TCRB registers, and counting proceeds

downward from the loaded value.

On the first underflow, the timer is loaded from the TCRA

register, then from the TCRB register on the next underflow,

then from the TCRA register again on the next underflow,

and so on. Every time the counter is stopped and restarted,

it always obtains its first reload value from the TCRA regis-

ter. This is true whether the timer is restarted upon reset, af-

ter entering Mode 1 from another mode, or after stopping

and restarting the clock with the Timer/Counter 1 clock se-

lector.

The timer can be configured to toggle the TA output bit on

each underflow. This generates a clock signal on the TA out-

put with the width and duty cycle determined by the values

stored in the TCRA and TCRB registers. This is a “proces-

sor-independent” PWM clock because once the timer is set

up, no more action is required from the CPU to generate a

continuous PWM signal.

The timer can be configured to generate separate interrupts

upon reload from the TCRA and TCRB registers. The inter-

rupts can be enabled or disabled under software control.

The CPU can determine the cause of each interrupt by look-

ing at the TAPND and TBPND bits, which are updated by

the hardware on each occurrence of a timer reload.

In Mode 1, Timer/Counter 2 (TCNT2) can be used either as

a simple system timer, an external event counter, or a pulse-

accumulate counter. The clock counts down using the clock

selected with the Timer/Counter 2 clock selector. It gener-

ates an interrupt upon each underflow if the interrupt is en-

abled with the TDIEN bit.

Figure 100.

Processor-Independent PWM Mode

Timer/Counter 1

TCNT1

Timer 1

Clock

Reload B = Time 2

TCRB

Reload A = Time 1

TCRA

TAPND

TBPND

TAIEN

Timer

Interrupt A

TAEN

TA

TB

TBIEN

Timer

Interrupt B

Underflow

Underflow

TDIEN

Timer

Interrupt D

TDPND

Timer/Counter 2

TCNT2

Timer 2

Clock

Clock

Selector

DS084