2 module status register (mstat), 3 software reset register (swreset), Module status register (mstat) – National CP3BT26 User Manual

Page 30: Software reset register (swreset), Cp3bt26

www.national.com

30

CP3BT26

7.2

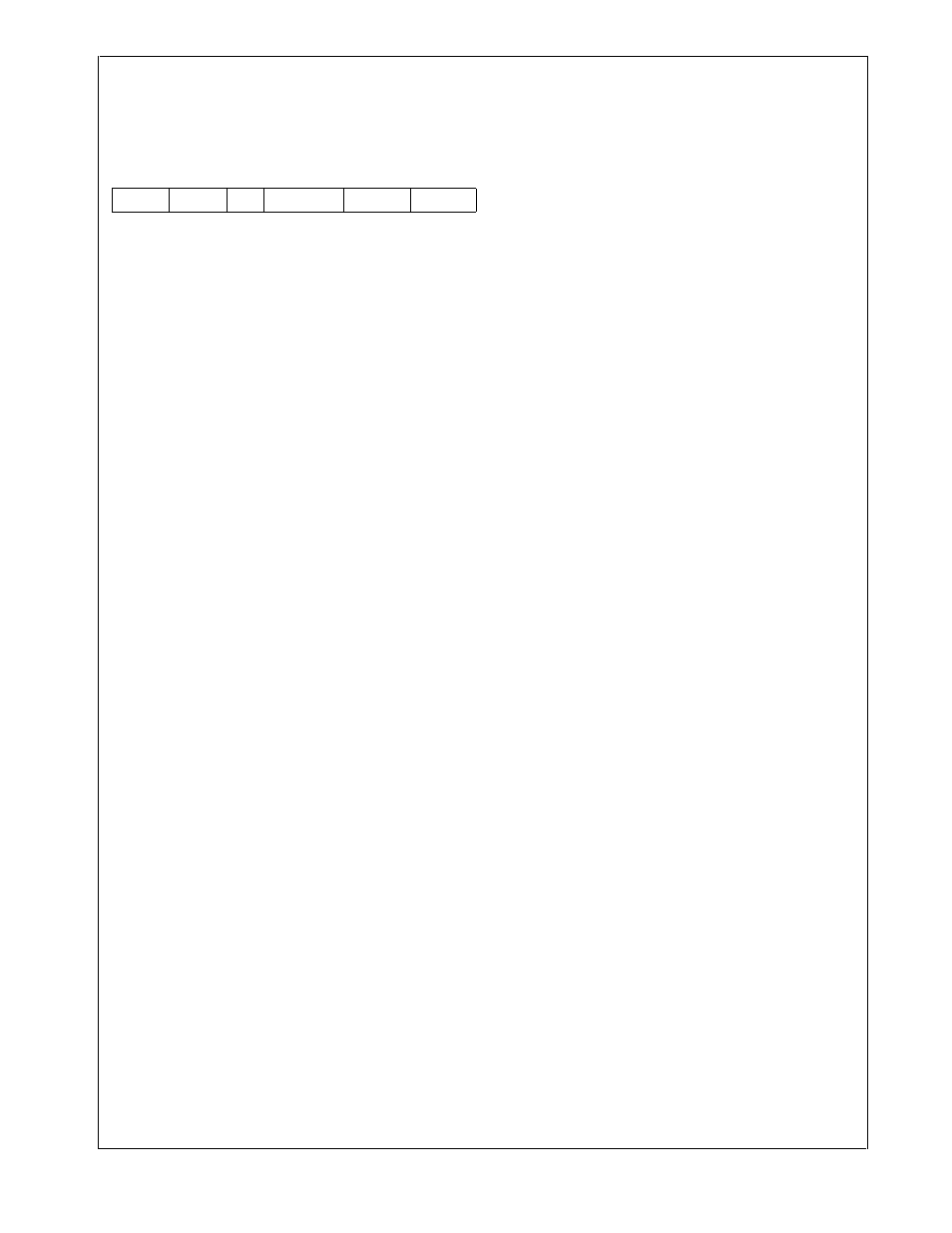

MODULE STATUS REGISTER (MSTAT)

The MSTAT register is a byte-wide, read-only register that

indicates the general status of the device. The MCFG regis-

ter format is shown below.

OENV2:0

The Operating Environment bits hold the

states sampled from the ENV[2:0] input pins

at reset. These states are controlled by exter-

nal hardware at reset and are held constant in

the register until the next reset.

PGMBUSY

The Flash Programming Busy bit is automati-

cally set when either the program memory or

the data memory is being programmed or

erased. It is clear when neither of the memo-

ries is busy. When this bit is set, software must

not attempt to program or erase either of

these two memories. This bit is a copy of the

FMBUSY bit in the FMSTAT register.

0

–

Flash memory is not busy.

1

–

Flash memory is busy.

DPGMBUSY The Data Flash Programming Busy indicates

that the flash data memory is being erased or

a pipelined programming sequence is current-

ly ongoing. Software must not attempt to per-

form any write access to the flash program

memory at this time, without also polling the

FSMSTAT.FMFULL bit in the flash memory in-

terface. The DPGMBUSY bit is a copy of the

FMBUSY bit in the FSMSTAT register.

0

–

Flash data memory is not busy.

1

–

Flash data memory is busy.

WDRST

The Watchdog Reset bit indicates that a

Watchdog timer reset has occurred. Write a 1

to this bit to clear it. Power-on reset also

clears this bit.

0

–

No Watchdog timer reset has occurred

since this bit was last cleared.

1

–

A Watchdog timer reset has occurred

since this bit was last cleared.

ISPRST

The Software ISP Reset bit indicates that a

software ISP reset has occurred since the bit

was last cleared. This bit is cleared by a

SWRESET(CLR) sequence or a power-on re-

set.

0

–

No software ISP reset has occurred since

this bit was last cleared.

1

–

A software ISP reset has occurred since

this bit was last cleared.

7.3

SOFTWARE RESET REGISTER

(SWRESET)

The SWRESET register is a byte-wide, write-only register

which provides a mechanism for software to initiate a reset

into ISP mode without regard to the status of the EMPTY

bits in the flash protection word. This form of reset is only al-

lowed when all of the following conditions are true:

The device is in IRE or ERE mode

BOOTAREA is defined (has a value other than 1111b) in

the Protection Word (see Section 8.4.2 for more details).

ISPE is set in the flash protection word, indicating that

there is ISP code in the flash

To initiate a reset under these conditions, it is necessary to

write the value E1h to the SWRESET register, followed with-

in 127 clock cycles by the value 3Eh. The reset then follows

immediately. This sequence is called SWRESET(ISP).

Once the device has been reset into ISP mode by SWRE-

SET(ISP), any subsequent reset (other than internal or ex-

ternal power-on reset) will cause the part to reset into ISP

mode because the EMPTY bits in the Protection Word con-

tinue to be ignored.

A second set of special values written to the SWRESET reg-

ister will cause a reset out of ISP mode (whether or not the

device is currently in ISP mode). This can be used as a sim-

ple software reset. In this case, no conditions are checked.

To initiate reset out of ISP mode, write the value E1h to the

SWRESET register, followed within 127 clock cycles by the

value 0Eh. The reset then follows immediately. This se-

quence is called SWRESET(CLR). This reset also cancels

the effect of any previous SWRESET(ISP), so subsequent

resets will check the EMPTY bits to determine whether to

enter ISP mode.

The ISP reset behaves similarly to the Watchdog reset, for

example, if the flash interface is busy when reset is assert-

ed, the reset to the clock module is delayed until the flash

operations are completed.

7

6

5

4

3

2

0

ISPRST WDRST Res. DPGMBUSY PGMBUSY OENV2:0