0 timing and watchdog module, 1 twm structure, 2 timer t0 operation – National CP3BT26 User Manual

Page 192: Timing and watchdog module, Twm structure, Timer t0 operation, Cp3bt26

www.national.com

192

CP3BT26

25.0 Timing and Watchdog Module

The Timing and Watchdog Module (TWM) generates the

clocks and interrupts used for timing periodic functions in

the system; it also provides Watchdog protection over soft-

ware execution.

The TWM is designed to provide flexibility in system design

by configuring various clock ratios and by selecting the

Watchdog clock source. After setting the TWM configura-

tion, software can lock it for a higher level of protection

against erroneous software action. Once the TWM is

locked, only reset can release it.

25.1

TWM STRUCTURE

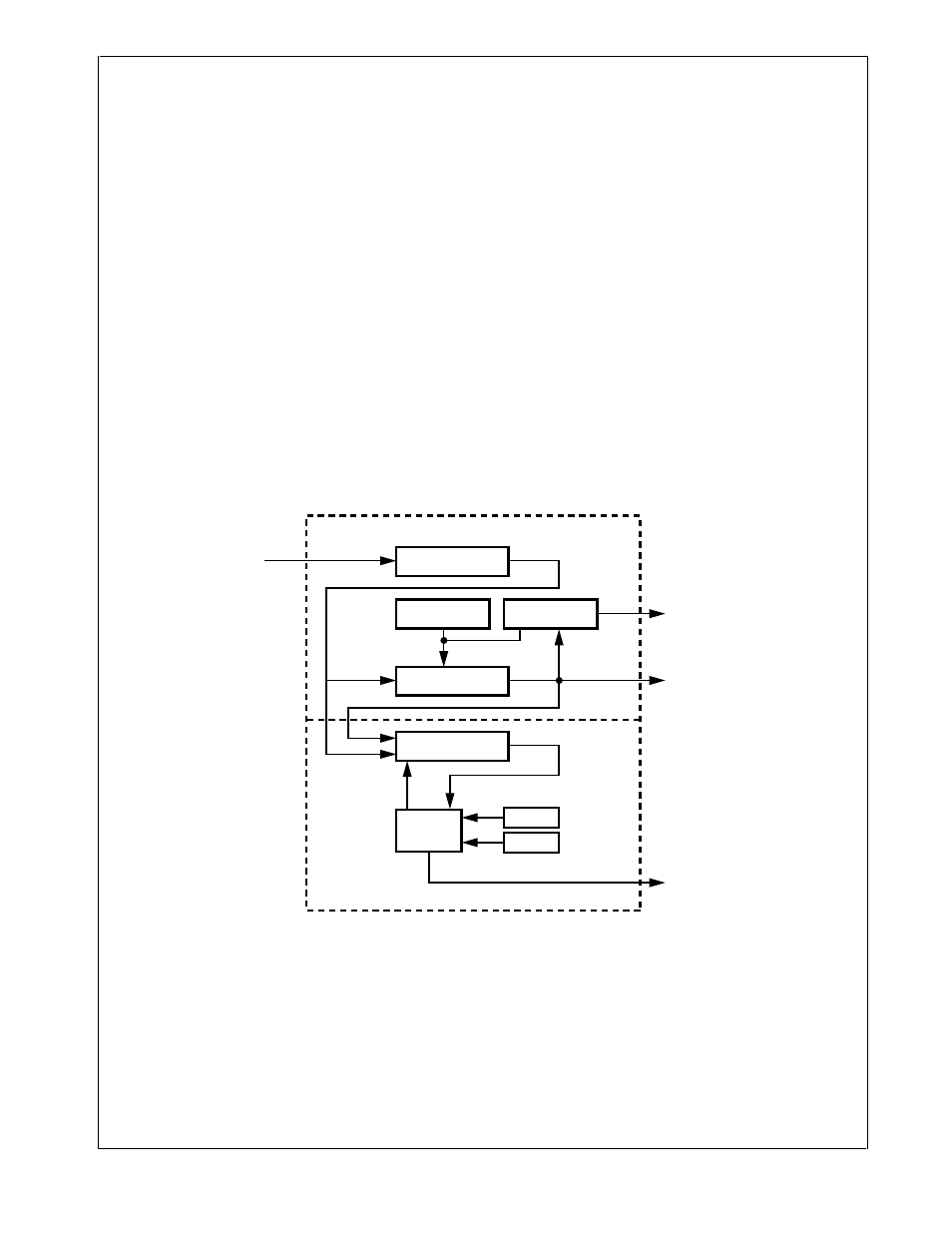

Figure 96 is a block diagram showing the internal structure

of the Timing and Watchdog module. There are two main

sections: the Real-Time Timer (T0) section at the top and

the Watchdog section on the bottom.

All counting activities of the module are based on the Slow

Clock (SLCLK). A prescaler counter divides this clock to

make a slower clock. The prescaler factor is defined by a 3-

bit field in the Timer and Watchdog Prescaler register, which

selects either 1, 2, 4, 8, 16, or 32 as the divisor. Therefore,

the prescaled clock period can be 2, 4, 8, 16, or 32 times the

Slow Clock period. The prescaled clock signal is called

T0IN.

25.2

TIMER T0 OPERATION

Timer T0 is a programmable 16-bit down counter that can

be used as the time base for real-time operations such as a

periodic audible tick. It can also be used to drive the Watch-

dog circuit.

The timer starts counting from the value loaded into the

TWMT0 register and counts down on each rising edge of

T0IN. When the timer reaches zero, it is automatically re-

loaded from the TWMT0 register and continues counting

down from that value. Therefore, the frequency of the timer

is:

When an external crystal oscillator is used as the SLCLK

source or when the fast clock is divided accordingly, f

SLCLK

is 32.768 kHz.

The value stored in TWMT0 can range from 0001h to

FFFFh.

Figure 96.

Timing and Watchdog Module Block Diagram

When the counter reaches zero, an internal timer signal

called T0OUT is set for one T0IN clock cycle. This signal

sets the TC bit in the TWMT0 Control and Status Register

(T0CSR). It also generates an interrupt (IRQ14), when en-

abled by the T0CSR.T0INTE bit. T0OUT is also an input to

the MIWU (see Section 13.0), so an edge-triggered inter-

rupt is also available through this alternative mechanism.

If software loads the TWMT0 register with a new value, the

timer uses that value the next time that it reloads the 16-bit

timer register (in other words, after reaching zero). Software

can restart the timer at any time (on the very next edge of

the T0IN clock) by setting the Restart (RST) bit in the

T0CSR register. The T0CSR.RST bit is cleared automati-

cally upon restart of the 16-bit timer.

Note: To enter Power Save or Idle mode after setting the

T0CSR.RST bit, software must wait for the reset operation

to complete before performing the switch.

f

TIMER

f

SLCLK

TWTM0

1

+

(

) prescaler

×

-----------------------------------------------------------------------

=

5-Bit Prescaler Counter

(TWCP)

REAL TIME TIMER (T0)

WATCHDOG

Restart

Restart

Underflow

Underflow

Slow

Clock

T0LINT

(to ICU)

T0OUT

(to Multi-Input-

Wake-Up)

WDERR

Watchdog Error

16-Bit Timer

(Timer0)

WATCHDOG

Timer

WATCHDOG

Service

Logic

TWW/MT0 Register

T0CSR Contrl. Reg.

WDSDM

WDCNT

DS080

T0IN