Cp3 bt26 – National CP3BT26 User Manual

Page 147

147

www.national.com

CP3

BT26

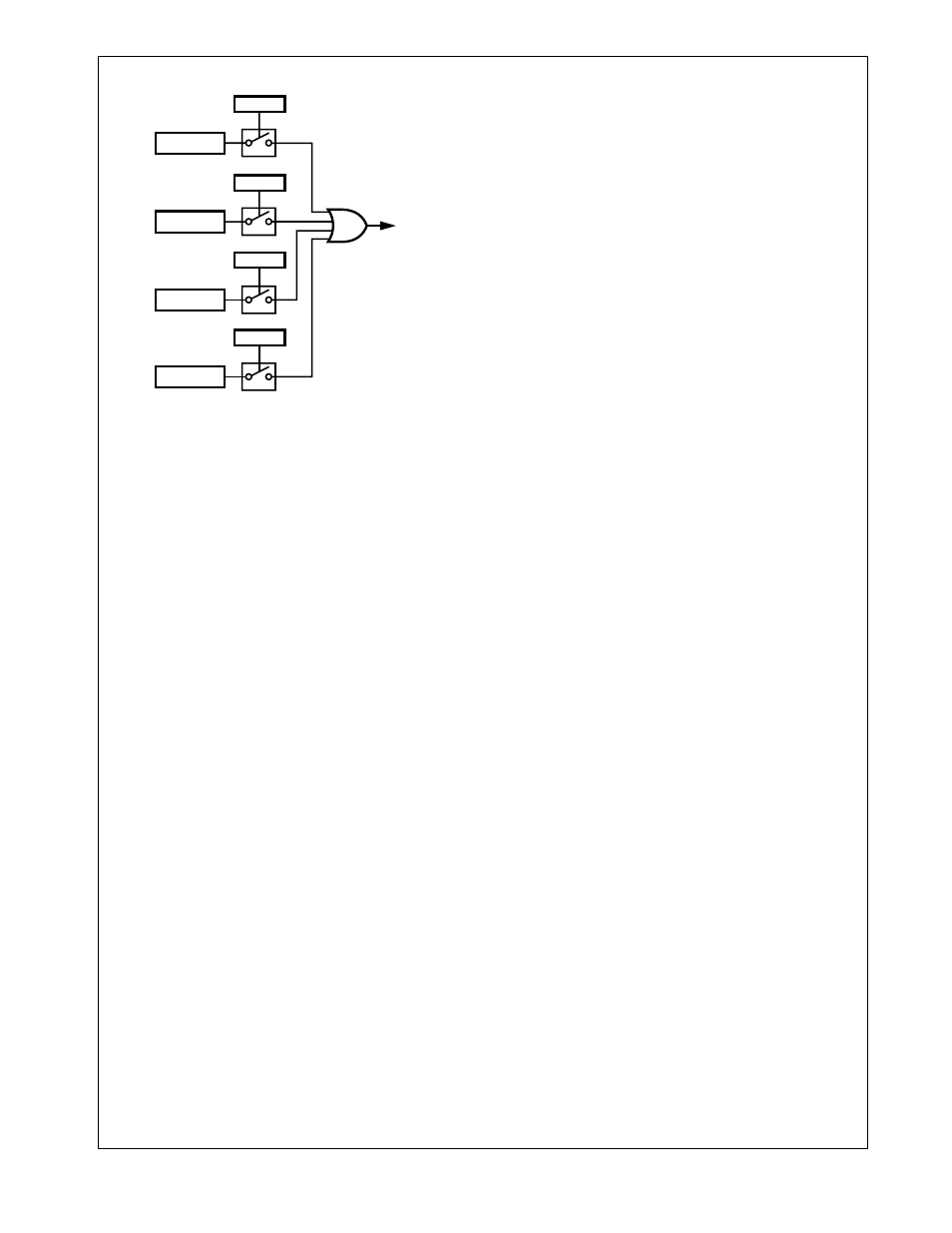

Figure 70 shows the interrupt structure of the AAI.

Figure 70.

AAI Interrupt Structure

20.5.3

Normal Mode

In normal mode, each frame sync signal marks the begin-

ning of a new frame and also the beginning of a new slot,

since each frame only consists of one slot. All 16 receive

and transmit FIFO locations hold data for the same (and

only) slot of a frame. If 8-bit data are transferred, only the

low byte of each 16-bit FIFO location holds valid data.

20.5.4

Transmit

Once the interface has been enabled, transmit transfers are

initiated automatically at the beginning of every frame. The

beginning of a new frame is identified by a frame sync pulse.

Following the frame sync pulse, the data is shifted out from

the ATSR to the STD pin on the positive edge of the transmit

data shift clock (SCK).

DMA Operation

When a complete data word has been transmitted through

the STD pin, a new data word is reloaded from the transmit

DMA register 0 (ATDR0). A DMA request is asserted when

the ATDR0 register is empty. If a new data word must be

transmitted while the ATDR0 register is still empty, the pre-

vious data will be re-transmitted.

FIFO Operation

When a complete data word has been transmitted through

the STD pin, a new data word is loaded from the transmit

FIFO from the current location of the Transmit FIFO Read

Pointer (TRP). After that, the TRP is automatically incre-

mented by 1.

A write to the Audio Transmit FIFO Register (ATFR) results

in a write to the transmit FIFO at the current location of the

Transmit FIFO Write Pointer (TWP). After every write oper-

ation to the transmit FIFO, TWP is automatically increment-

ed by 1.

When the TRP is equal to the TWP and the last access to

the FIFO was a read operation (a transfer to the ATSR), the

transmit FIFO is empty. When an additional read operation

from the FIFO to ATSR is performed (while the FIFO is al-

ready empty), a transmit FIFO underrun occurs. In this

event, the read pointer (TRP) will be decremented by 1 (in-

cremented by 15) and the previous data word will be trans-

mitted again. A transmit FIFO underrun is indicated by the

TXU bit in the Audio Interface Transmit Status and Control

Register (ATSCR). Also, no transmit interrupt will be gener-

ated (even if enabled).

When the TRP is equal to the TWP and the last access to

the FIFO was a write operation (to the ATFR), the FIFO is

full. If an additional write to ATFR is performed, a transmit

FIFO overrun occurs. This error condition is not prevented

by hardware. Software must ensure that no transmit overrun

occurs.

The transmit frame synchronization pulse on the SFS pin

and the transmit shift clock on the SCK pin may be generat-

ed internally, or they can be supplied by an external source.

20.5.5

Receive

At the receiver, the received data on the SRD pin is shifted

into ARSR on the negative edge of SRCLK (or SCK in syn-

chronous mode), following the receive frame sync pulse,

SRFS (or SFS in synchronous mode).

DMA Operation

When a complete data word has been received through the

SRD pin, the new data word is copied to the receive DMA

register 0 (ARDR0). A DMA request is asserted when the

ARDR0 register is full. If a new data word is received while

the ARDR0 register is still full, the ARDR0 register will be

overwritten with the new data.

FIFO Operation

When a complete word has been received, it is transferred

to the receive FIFO at the current location of the Receive

FIFO Write Pointer (RWP). Then, the RWP is automatically

incremented by 1.

A read from the Audio Receive FIFO Register (ARFR) re-

sults in a read from the receive FIFO at the current location

of the Receive FIFO Read Pointer (RRP). After every read

operation from the receive FIFO, the RRP is automatically

incremented by 1.

When the RRP is equal to the RWP and the last access to

the FIFO was a copy operation from the ARFR, the receive

FIFO is full. When a new complete data word has been shift-

ed into ARSR while the receive FIFO was already full, the

shift register overruns. In this case, the new data in the

ARSR will not be copied into the FIFO and the RWP will not

be incremented. A receive FIFO overrun is indicated by the

RXO bit in the Audio Interface Receive Status and Control

Register (ARSCR). No receive interrupt will be generated

(even if enabled).

When the RWP is equal to the RRP and the last access to

the receive FIFO was a read from the ARFR, a receive FIFO

underrun has occurred. This error condition is not prevented

by hardware. Software must ensure that no receive under-

run occurs.

The receive frame synchronization pulse on the SRFS pin

(or SFS in synchronous mode) and the receive shift clock on

the SRCLK (or SCK in synchronous mode) may be gener-

ated internally, or they can be supplied by an external

source.

AAI

Interrupt

RXEIP = 1

RXEIE

TXIP = 1

TXIE

TXEIP = 1

TXEIE

DS155

RXIP = 1

RXIE