Cp3bt26 – National CP3BT26 User Manual

Page 70

www.national.com

70

CP3BT26

14.1.6

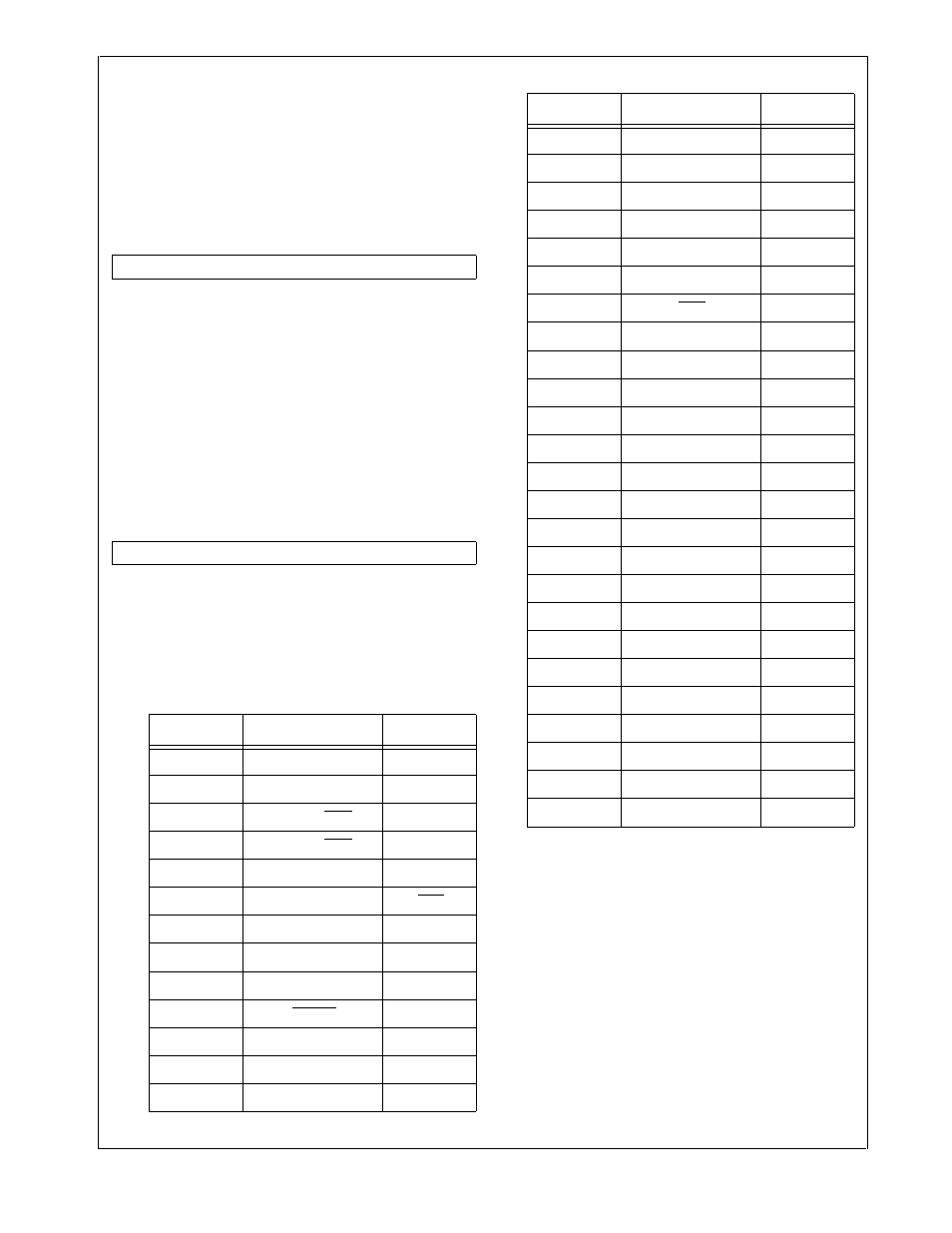

Port High Drive Strength Register (PxHDRV)

The PxHDRV register is a byte-wide, read/write register that

controls the slew rate of the corresponding pins. The high

drive strength function is enabled when the corresponding

bits of the PxHDRV register are set. In both GPIO and alter-

nate function modes, the drive strength function is enabled

by the PxHDRV registers. At reset, the PxHDRV registers

are cleared, making the ports low speed.

PxHDRV

The PxHDRV bits control whether output pins

are driven with slow or fast slew rate.

0

–

Slow slew rate.

1

–

Fast slew rate.

14.1.7

Port Alternate Function Select Register

(PxALTS)

The PxALTS register selects which of two alternate func-

tions are selected for the port pin. These bits are ignored

unless the corresponding PxALT bits are set. Each port pin

can be controlled independently.

PxALTS

The PxALTS bits select among two alternate

functions. Table 30 shows the mapping of the

PxALTS bits to the alternate functions. Un-

used PxALTS bits must be clear.

7

0

PxHDRV

7

0

PxALTS

Table 30

Alternate Function Select

Port Pin

PxALTS = 0

PxALTS = 1

PE0

UART0 RXD0

Reserved

PE1

UART0 TXD0

Reserved

PE2

UART0 RTS

Reserved

PE3

UART0 CTS

Reserved

PE4

UART0 CKX

TB

PE5

SRFS

NMI

PF0

MSK

TIO1

PF1

MDIDO

TIO2

PF2

MDODI

TIO3

PF3

MWCS

TIO4

PF4

SCK

TIO5

PF5

SFS

TIO6

PF6

STD

TIO7

PF7

SRD

TIO8

PG0

RFSYNC

Reserved

PG1

RFCE

Reserved

PG2

BTSEQ1

SRCLK

PG3

SCLK

Reserved

PG4

SDAT

Reserved

PG5

SLE

Reserved

PG6

WUI10

BTSEQ2

PG7

TA

BTSEQ3

PH0

UART1 RXD1

WUI11

PH1

UART1 TXD1

WUI12

PH2

UART2 RXD2

WUI13

PH3

UART2 TXD2

WUI14

PH4

UART3 RXD3

WUI15

PH5

UART3 TXD3

WUI16

PH6

CANRX

WUI17

PH7

CANTX

Reserved

PJ0

WUI18

Reserved

PJ1

WUI19

Reserved

PJ2

WUI20

Reserved

PJ3

WUI21

Reserved

PJ4

WUI22

Reserved

PJ5

WUI23

Reserved

PJ6

WUI24

Reserved

PJ7

ASYNC

WUI9

Table 30

Alternate Function Select

Port Pin

PxALTS = 0

PxALTS = 1