3 watchdog operation, 4 twm registers, Watchdog operation – National CP3BT26 User Manual

Page 193: Twm registers, Cp3 bt26

193

www.national.com

CP3

BT26

25.3

WATCHDOG OPERATION

The Watchdog is an 8-bit down counter that operates on the

rising edge of a specified clock source. At reset, the Watch-

dog is disabled; it does not count and no Watchdog signal is

generated. A write to either the Watchdog Count (WDCNT)

register or the Watchdog Service Data Match (WDSDM)

register starts the counter. The Watchdog counter counts

down from the value programmed in the WDCNT register.

Once started, only a reset can stop the Watchdog from op-

erating.

The Watchdog can be programmed to use either T0OUT or

T0IN as its clock source (the output and input of Timer T0,

respectively). The TWCFG.WDCT0I bit controls this clock

selection.

Software must periodically “service” the Watchdog. There

are two ways to service the Watchdog, the choice depend-

ing on the programmed value of the WDSDME bit in the

Timer and Watchdog Configuration (TWCFG) register.

If the TWCFG.WDSDME bit is clear, the Watchdog is ser-

viced by writing a value to the WDCNT register. The value

written to the register is reloaded into the Watchdog counter.

The counter then continues counting down from that value.

If the TWCFG.WDSDME bit is set, the Watchdog is ser-

viced by writing the value 5Ch to the Watchdog Service

Data Match (WDSDM) register. This reloads the Watchdog

counter with the value previously programmed into the WD-

CNT register. The counter then continues counting down

from that value.

A Watchdog error signal is generated by any of the following

events:

The Watchdog serviced too late.

The Watchdog serviced too often.

The WDSDM register is written with a value other than

5Ch when WDSDM type servicing is enabled

(TWCFG.WDSDME = 1).

A Watchdog error condition resets the device.

25.3.1

Register Locking

The Timer and Watchdog Configuration (TWCFG) register

is used to set the Watchdog configuration. It controls the

Watchdog clock source (T0IN or T0OUT), the type of

Watchdog servicing (using WDCNT or WDSDM), and the

locking state of the TWCFG, TWCPR, TIMER0, T0CSR,

and WDCNT registers. A register that is locked cannot be

read or written. A write operation is ignored and a read op-

eration returns unpredictable results.

If the TWCFG register is itself locked, it remains locked until

the device is reset. Any other locked registers also remain

locked until the device is reset. This feature prevents a run-

away program from tampering with the programmed Watch-

dog function.

25.3.2

Power Save Mode Operation

The Timer and Watchdog Module is active in both the Power

Save and Idle modes. The clocks and counters continue to

operate normally in these modes. The WDSDM register is

accessible in the Power Save and Idle modes, but the other

TWM registers are accessible only in the Active mode.

Therefore, Watchdog servicing must be carried out using

the WDSDM register in the Power Save or Idle mode.

In the Halt mode, the entire device is frozen, including the

Timer and Watchdog Module. On return to Active mode, op-

eration of the module resumes at the point at which it was

stopped.

Note: After a restart or Watchdog service through WDCNT,

do not enter Power Save mode for a period equivalent to 5

Slow Clock cycles.

25.4

TWM REGISTERS

The TWM registers controls the operation of the Timing and

Watchdog Module. There are six such registers:

The WDSDM register is accessible in both Active and Pow-

er Save mode. The other TWM registers are accessible only

in Active mode.

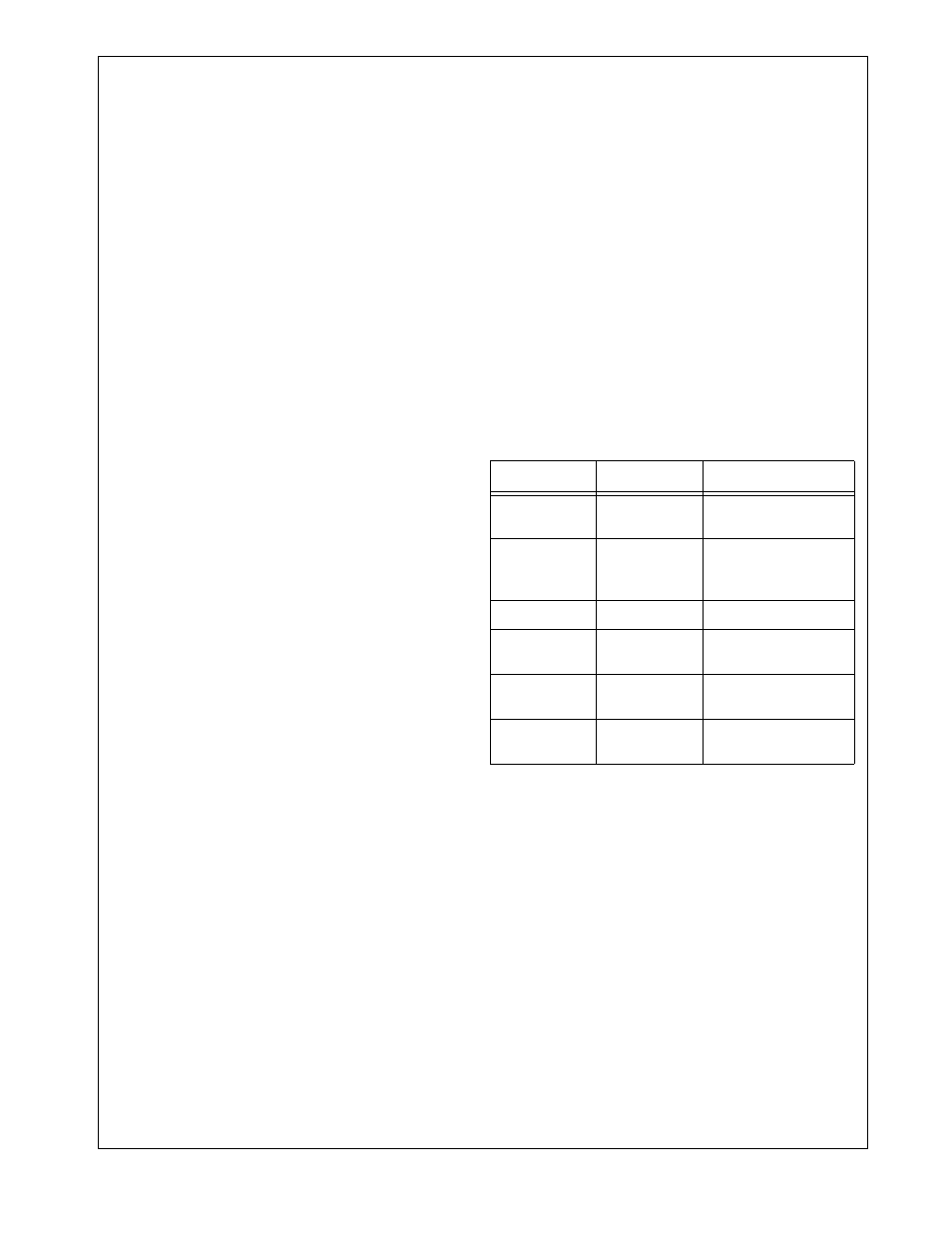

Table 76

TWM Registers

Name

Address

Description

TWCFG

FF FF20h

Timer and Watchdog

Configuration Register

TWCP

FF FF22h

Timer and Watchdog

Clock Prescaler

Register

TWMT0

FF FF24h

TWM Timer 0 Register

T0CSR

FF FF26h

TWMT0 Control and

Status Register

WDCNT

FF FF28h

Watchdog Count

Register

WDSDM

FF FF2Ah

Watchdog Service

Data Match Register