Nortel Networks NN43001-301 User Manual

Page 71

NT5D12 Dual-port DTI/PRI

71

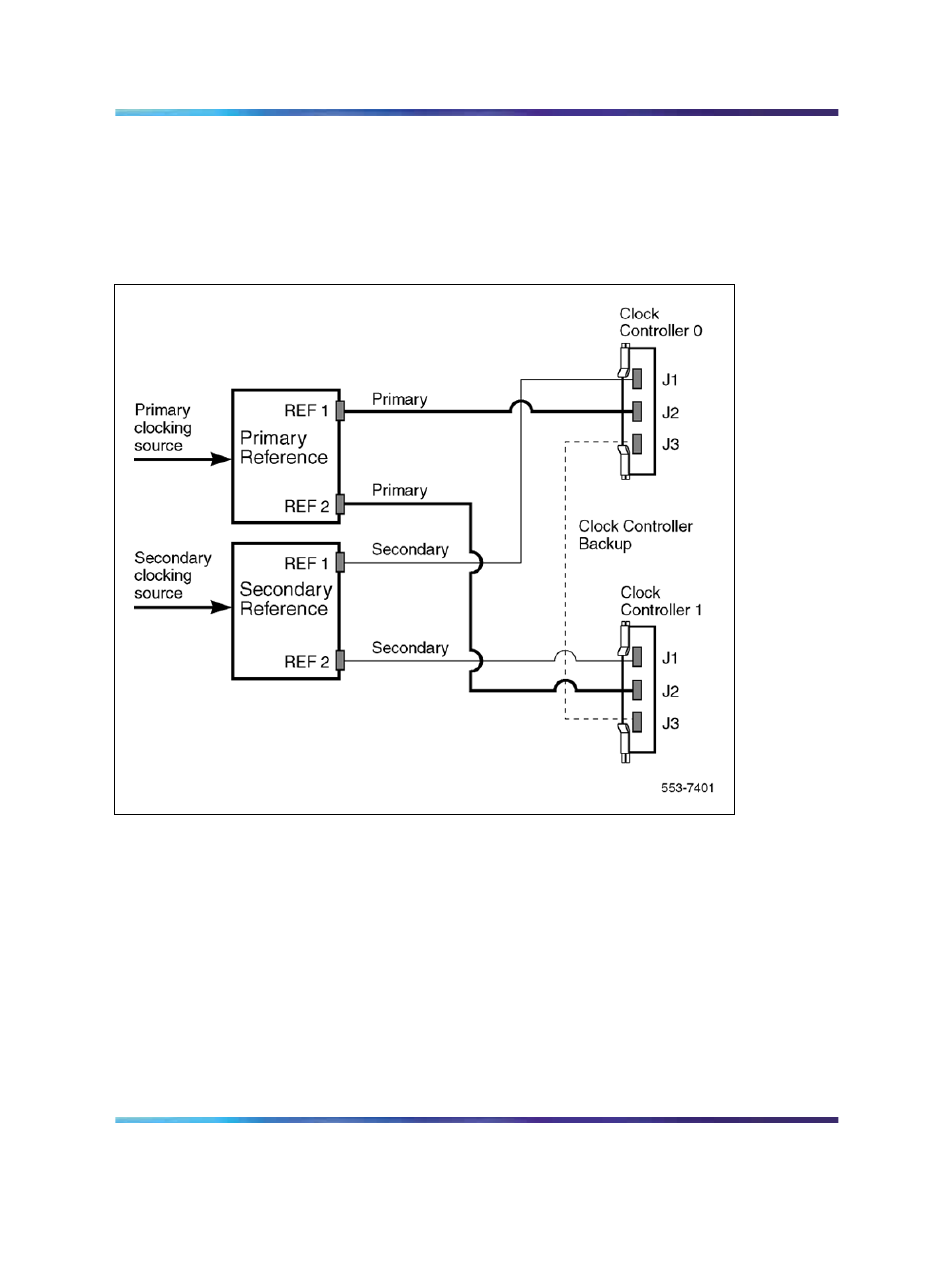

As shown in

Figure 30 "Clock Controller primary and secondary tracking"

, a system with dual CPUs can have two clock controllers (CC-0

and CC-1). One clock controller acts as a back-up to the other. Lock the

clock controllers to the reference clock.

Figure 30

Clock Controller primary and secondary tracking

Free run (non-tracking) mode

The clock synchronization of the system can operate in free-run mode if:

•

no loop is defined as the primary or secondary clock reference,

•

the primary and secondary references are disabled, or

•

the primary and secondary references are in local (near end) alarm.

Reference clock errors

The system software checks at intervals of 1 to 15 minutes to see if a clock

controller or reference-clock error has occurred. (The interval of this check

can be configured in LD 73.)

Nortel Communication Server 1000

ISDN Primary Rate Interface Installation and Commissioning

NN43001-301

02.03

Standard

Release 5.5

7 December 2007

Copyright © 2003-2007, Nortel Networks

.