Altera POS-PHY Level 4 IP Core User Manual

Page 95

Chapter 5: Functional Description—Transmitter

5–25

Avalon-MM Interface Register Map

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

1

If the hitless bandwidth repositioning (HBWR) register is not enabled, the CALM1,

CALLEN1

, CALMEM_DAT registers become reserved.

1

Only change the CALM0, CALLEN0, CALMEM_DAT0 registers when the DISABLED register is

equal to 1, or when the CALSEL_ACT register is equal to 1. Only change the CALM1,

CALLEN1

, CALMEM_DAT1 registers when the DISABLED register is equal to 1, or when the

CALSEL_ACT

register is equal to 0.

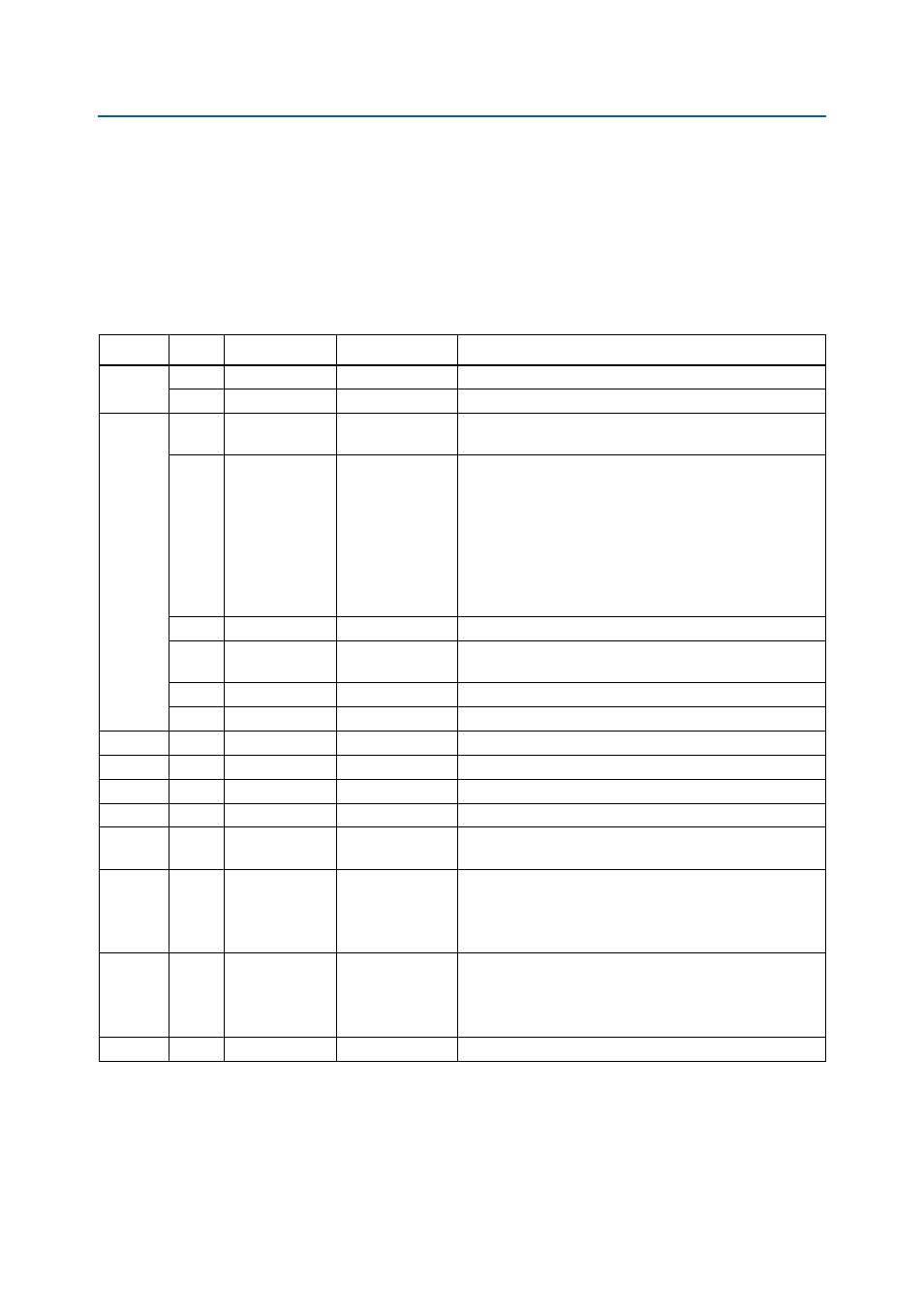

Table 5–10. Avalon-MM Interface Register Map

Address

Bits

Name

Type

Description

0

12:0

AOT_ID

Read only status

AOT code

15:13

BLOCK_ID

Read only status

Block ID

1

0

HBWR_EN

Read write control

HBWR_EN

enables the calendar select word in the status

frame.

1

RSFRM

Read write control

RSFRM

disables the status finite state machine. This forces

stat_ts_sync

low and stat_ts_disabled high at the end

of the current status frame. Regular behavior eventually

resumes after this bit is cleared. The value of the register is

OR

ed with the ctl_ts_rsfrm input.

This bit resets to one. Therefore, you must reprogram the

calendar and clear this bit whenever the IP core is reset.

2

RESERVED

Reserved Reserved.

3

CALSEL_ACT

Read only status

CALSEL_ACT

is the active calendar select word. 0='b01,

1='b10

4

SYNC

Read only status

Mirror of stat_ts_sync.

5

DISABLED

Read only status

Mirror of stat_ts_disabled.

2

7:0

CALM0

Read write control

CALM

when CALSEL_ACT=0.

3

7:0

CALM1

Read write control

CALM

when CALSEL_ACT=1.

4

9:0

CALLEN0

Read write control

CALLEN

when CALSEL_ACT=0.

5

9:0

CALLEN1

Read write control

CALLEN

when CALSEL_ACT=1.

6

9:0

CALMEM_ADR

Read write indirect

control

Refer to CALMEM_DAT0 and CALMEM_DAT1.

7

7:0

CALMEM_DAT0

Read write indirect

data

If write, then CALMEM_ADR is applied to the write address of

RAM with CALMEM_DAT0 applied to the write data.

If read, then CALMEM_ADR is applied to the read address of

RAM, and resulting read data is captured in CALMEM_DAT0.

8

7:0

CALMEM_DAT1

Read write indirect

data

If write, then CALMEM_ADR is applied to the write address of

RAM with CALMEM_DAT1 applied to the write data.

If read, then CALMEM_ADR is applied to the read address of

RAM, and resulting read data is captured in CALMEM_DAT1.

9..15 —

RESERVED

Reserved Reserved.