Atlantic interface error detection and handling – Altera POS-PHY Level 4 IP Core User Manual

Page 84

5–14

Chapter 5: Functional Description—Transmitter

Error Flagging and Handling

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

Table 5–2

summarizes the SPI-4.2 protocol errors.

Atlantic Interface Error Detection and Handling

When the Atlantic error checking parameter is turned on, a filtering block—the

Atlantic FIFO buffer error checker—is instantiated at the write side of the FIFO buffer

to ensure that only valid packets are written into memory.

The Atlantic FIFO buffer error checker block checks for missing SOP and EOP

markers, for each port. If these markers are found to be missing, their respective

err_aN_msopN

and err_aN_meopN signals are asserted and the packet is corrected.

These signals remain high for one aN_atxclk cycle. These error conditions do not

correlate directly—in terms of latency—to the data coming out of the FIFO buffer.

When a missing SOP error is detected, the Atlantic FIFO error checker block asserts

the err_aN_msopN flag and filters the burst. Data following a missing SOP is ignored

for that port until a SOP is detected.

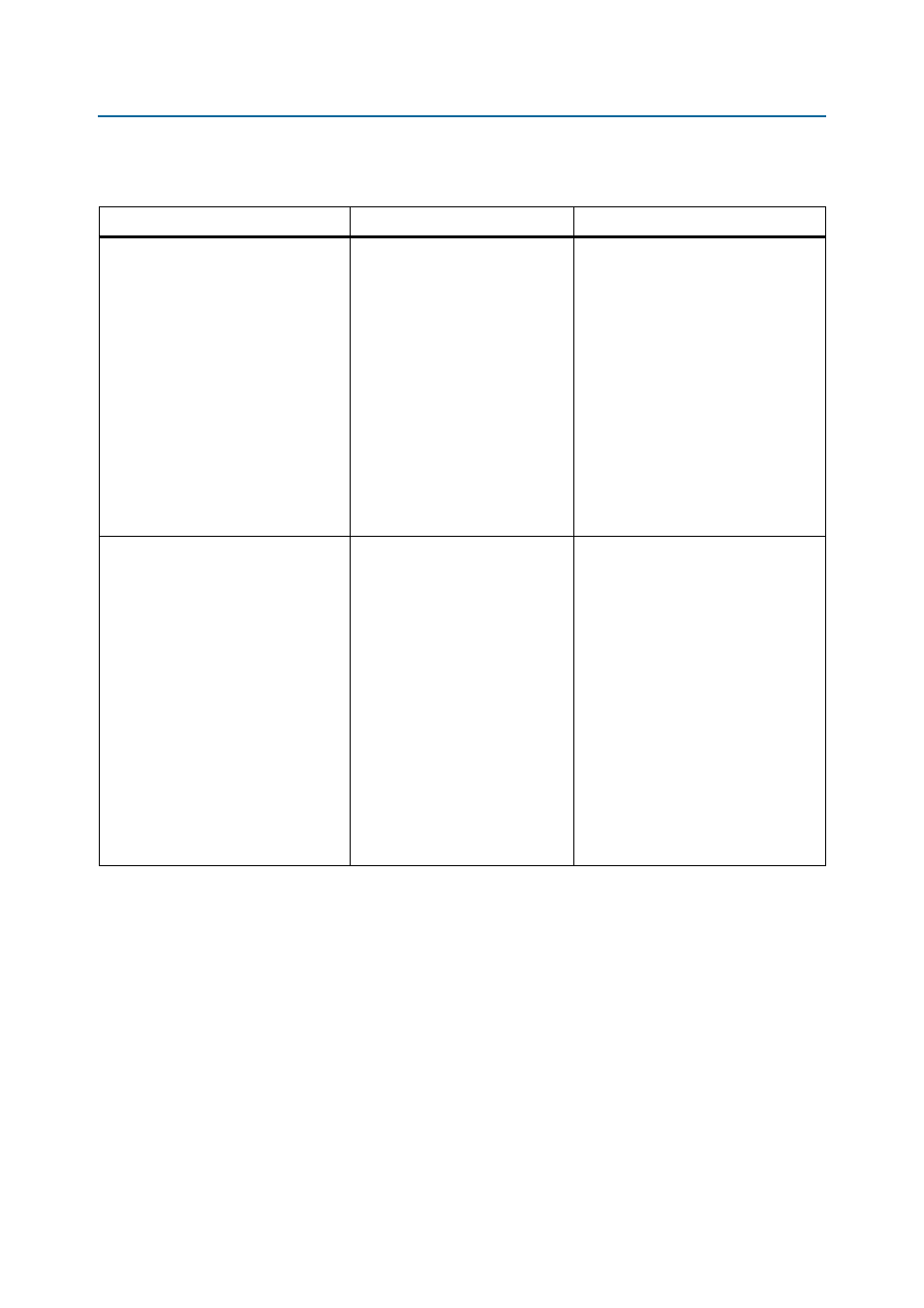

Table 5–2. SPI-4.2 Protocol Error Handling

Error

Condition

Response

Single DIP-2 or frame error has been

detected

Assuming the bad_level input is greater

than 1 (ctl_ts_sync_bad_theshold)

Bit error on bus

■

When stat_ts_sync is asserted,

assert err_ts_dip2.

■

stat_ts_sync

remains asserted

(high).

■

Transmit output data (TDAT) is

unaffected.

■

For pessimistic mode, the received

calendar status is ignored, the status

is not forwarded to the user logic, and

the transmit scheduler is not updated

with new credits.

■

For optimistic mode, no action is

taken. An incorrect status value may

be extracted and passed on to the

scheduler.

Multiple consecutive DIP-2 or frame

errors when sync is detected

Causes the bad_level counter to go over

the bad level threshold

(ctl_ts_sync_bad_theshold)

■

Bit errors on bus

■

Incorrect status edge

■

Calendar multiplier and

Maximum calendar length

values do not match the far-end

values

■

Receiver is sending incorrect

calendar multiplier or calendar

length values

■

Receiver sending corrupted

status frames

■

When stat_ts_sync is asserted, the

scheduler ignores a value of 11.

■

When stat_ts_sync is not asserted,

the state machine returns to the

disabled state and waits for the next

framing pattern.

■

All credits are revoked.

■

Data stops transmitting on the nearest

burst unit size boundary or EOP.

■

Training patterns are sent

continuously.

■

The data in the buffer is untouched.

■

Once the status channel regains sync,

the transmitter restarts, and packet

transfers resume from where they left

off (that is, continue open packets).