Altera POS-PHY Level 4 IP Core User Manual

Page 92

5–22

Chapter 5: Functional Description—Transmitter

Signals

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

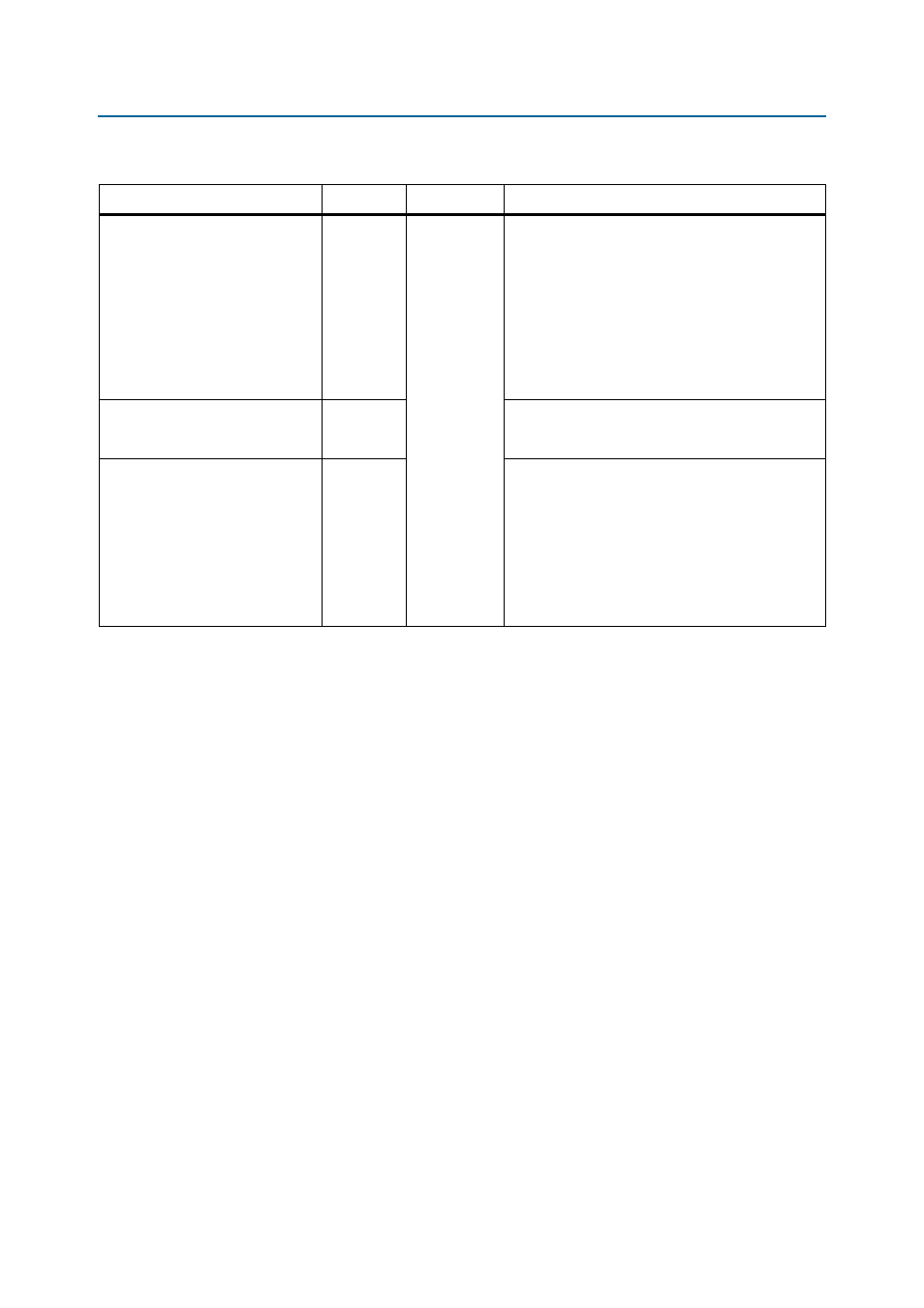

Table 5–8. Data Path and Control Status (Part 1 of 2)

Signal

Direction

Clock Domain

Description

ctl_td_holb_disable

Input- Static

reset

tdint_clk

Head-of-line blocking disable. When set to logic 1,

the data path requests data from the scheduler or

Atlantic buffer(s) whenever possible. When set to

logic 0, status (after error checking) is monitored for

all ports, and while any port is satisfied, the

transmitter stops requesting data from the scheduler

or Atlantic buffer(s), and sends idle control words or

training patterns. This input is tied to one in the IP

Toolbench top-level file, if you use the individual

buffers mode. Only change at reset.

stat_td_holb

Output

Indicates if the IP core is currently head-of-line

blocked. It is never asserted if

ctl_td_holb_disable

is set to logic 1.

ctl_td_maxt[15:0]

Input

Training sequence interval, measured from the end of

the last training sequence to the beginning of the next

training sequence. The actual interval may be slightly

longer to maintain valid bursts according to

ctl_td_burstlen

. Setting to zero disables interval

training insertion. Training is always inserted if

stat_ts_sync

is deasserted. Training patterns

always begin on the positive edge of tdclk. Only

change at reset.