C. optimum frequency for rxsys_clk, Of the, Appendix c – Altera POS-PHY Level 4 IP Core User Manual

Page 115: Optimum frequency for rxsys_clk, Chapter c, optimum, Frequency for rxsys_clk

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

C. Optimum Frequency for rxsys_clk

The IP core’s protocol logic and all Atlantic FIFO buffers share a common clock called

rxsys_clk

that clocks both the write and read sides of the Atlantic FIFO buffers.

Table C–1

shows the rxsys_clk clock frequency restrictions.

Restriction (a) is imposed by the SOP alignment block, which moves the SOP for each

packet into the first-byte position. This move slows the pipeline and temporarily fills

up the alignment buffer. If the higher frequency requirement is not met, the alignment

buffer may overflow. To guarantee correct system operation, the smallest expected

packet size should be used, and the assumption that the IP core is receiving a constant

stream of packets is made.

Restriction (b) comes from the status generation. The IP core requires one clock cycle

more than the length of the status frame to generate a status frame. This cycle is added

on the rxsys_clk domain, thus it must be faster than rsclk. If this requirement is not

met, the IP core does not operate correctly, err_ry_stat_fifo is asserted periodically,

and the status generated is invalid. The worst case is the minimum length status

frame which is three cycles long, giving a ratio of 4/3.

For example, consider a 128-bit IP core with an LVDS data rate of 800 Mbps, using a

single port, a calendar length of 1, and a calendar multiple of 1. For this example,

rdint_clk

= rsclk = 100 MHz.

For a minimum packet size of 48 bytes, the required frequency for rxsys_clk from

restriction (a) is:

C1 = (48 +2) /16 = 3.125

Required rxsys_clk frequency [Ceiling (3.1251) / 3.125] × 100 = (4/3.125) × 100

= 128 MHz

The required frequency from restriction (b) is:

Status Frame Length = 3

rxsys_clk

frequency 100 × (3+1) /3 = 100 × 4/3 = 133.34 MHz

For this example, rxsys_clk 133.34 MHz

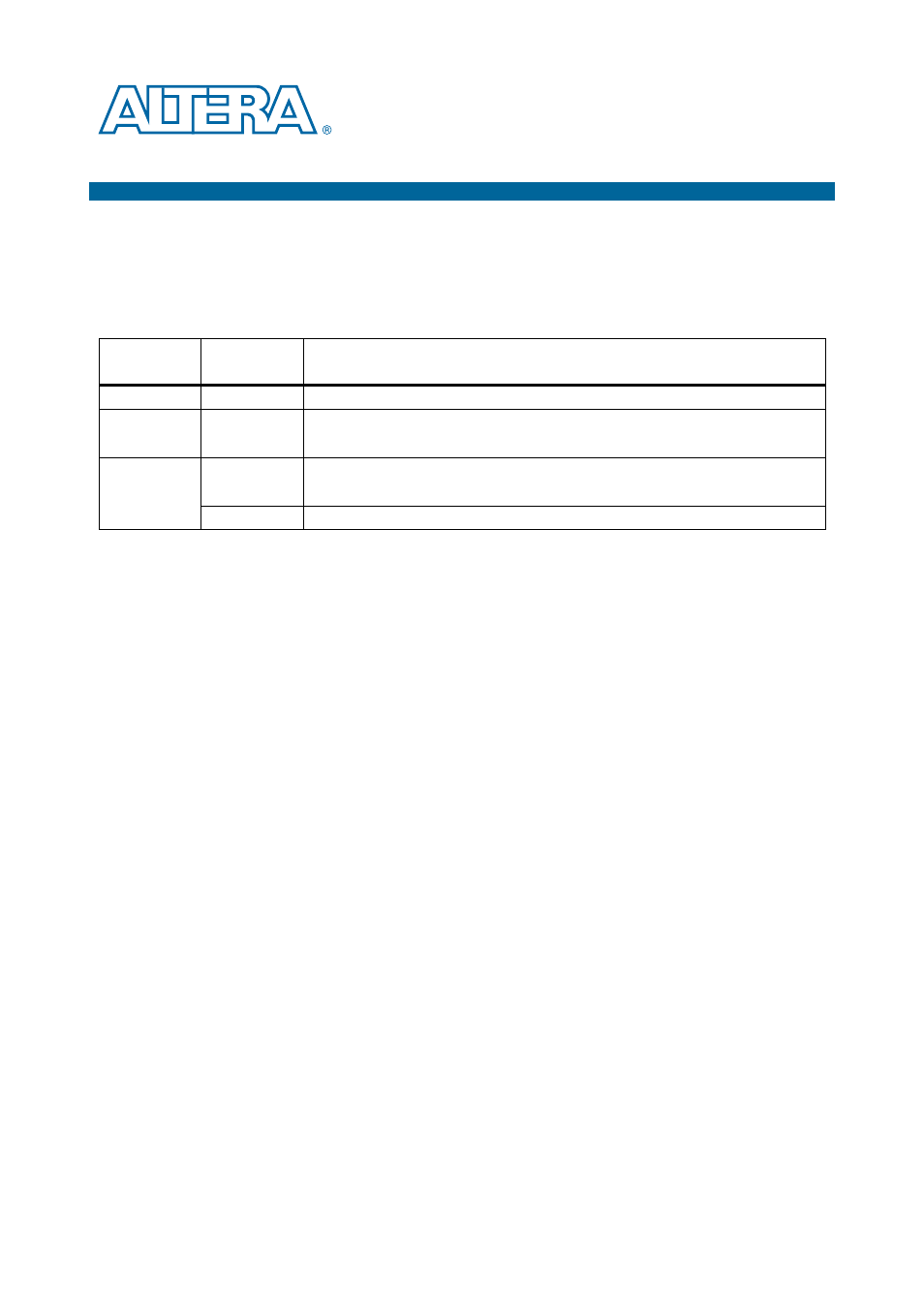

Table C–1. rxsys_clk Frequency Restrictions

Data Path

Width (Bits)

Restriction

Label

Restriction

32

a

rxsys_clk

frequency

rdint_clk frequency

64

a

rxsys_clk

frequency

[Ceiling (C1) / C1] × rdint_clk frequency

where C1 = (Packet Length +2)/8

(1)

128

a

rxsys_clk

frequency

(Ceiling (C1, 1) / C1) × rdint_clk frequency

where C1 = (Packet Length +2)/16

(1)

b

rxsys_clk

frequency

rsclk × (Status Frame Length + 1)/(Status Frame Length)

Note to

Table C–1

:

(1) For packet lengths

16 bytes, C1 = 1.