Altera POS-PHY Level 4 IP Core User Manual

Page 63

Chapter 4: Functional Description—Receiver

4–25

Signals

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

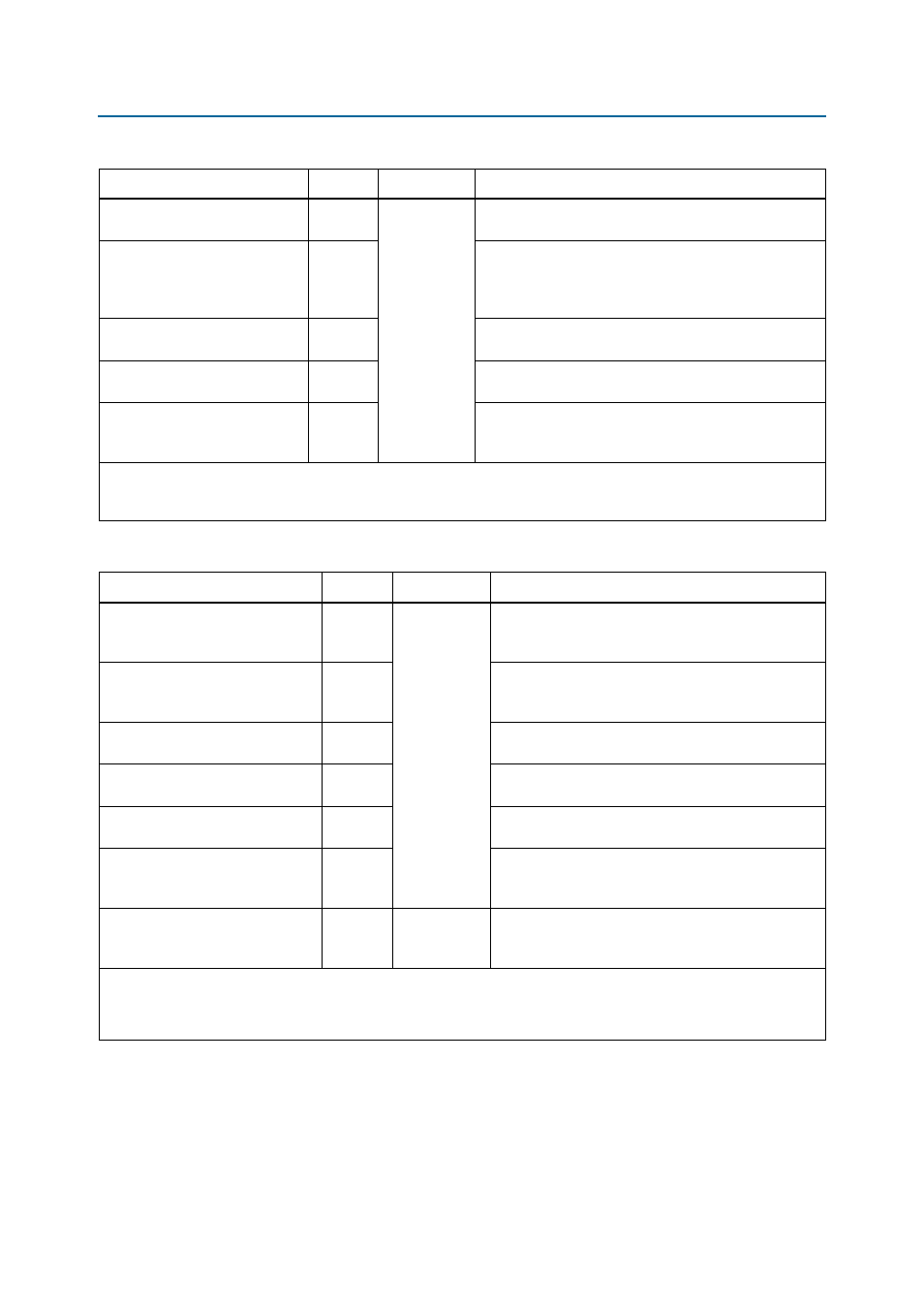

err_ry_fifo_oflwN

Output

rxsys_clk

Indicates that the FIFO buffer has overflowed, and data has

been lost (one for each Atlantic interface).

ctl_ry_errchk_chkpkt

Input –

Static

reset

Atlantic FIFO error checking enable. Disable to ignore

missing SOP and missing EOP detection and correction.

Value applies to all Atlantic buffer levels. Only change at

reset.

err_ry_msopN

Output

Indicates a packet was received on the SPI-4.2 bus with a

missing start of packet (one for each Atlantic buffer).

err_ry_meopN

Output

Indicates a packet was received on the SPI-4.2 bus with a

missing end of packet (one for each Atlantic buffer).

stat_ry_mp_erradr[7:0]

Output

Address qualifier for err_ry_meop and err_ry_msop

flags. Only present for the shared buffer with embedded

addressing mode.

Note to

Table 4–8

:

(1) For 128-and 64-bit variations, N is equal to log2(buffer size /(data path width × 16). For 32-bit variations, N is equal to log2(buffer size/data

path width×8).

Table 4–8. Atlantic FIFO Buffer Control and Status (Part 2 of 2)

Signal

Direction

Clock Domain

Description

Table 4–9. SPI-4.2 Channel Control and Status (Part 1 of 3)

Signal

Direction

Clock Domain

Description

ctl_ry_ae[n:0]

Input

rxsys_clk

Almost empty defines starving to hungry threshold.

Units are in bytes. Value applies to all Atlantic buffers.

Only change at reset.

ctl_ry_af[n:0]

Input

Almost full defines hungry to satisfied threshold. Units

are in bytes. Value applies to all Atlantic buffers. Only

change at reset.

ctl_ry_fifostatoverride

Input -

Static

Asserting this signal allows external logic to control the

outgoing status of each port. Only change at reset.

ctl_ry_extstat_val

Input

Valid qualifier for the external status input. This value is

ignored if ctl_ry_fifostatoverride is deasserted.

ctl_ry_extstat_adr[7:0]

Input

Port number for the external status value. This value is

ignored if ctl_ry_fifostatoverride is deasserted.

ctl_ry_extstat[1:0]

Input

Status for port indicated by ctl_ry_extstat_adr.

This value is ignored if ctl_ry_fifostatoverride is

deasserted.

ctl_rs_statedge

Input -

Static

constant

rsclk

Controls the edge of rsclk on which transitions of

rstat

occur. (1 = positive edge, 0 = negative edge).

Only change at reset.

Note to

:

(1) The external status address you provide does not have to be incrementing or have any set sequence. You can provide any address value, at any

time. If the external address provided is for an unprovisioned port, the value is written into the internal RAM at that address, but the internal

status block never reads from that location.