Fifo ram blocks – Altera POS-PHY Level 4 IP Core User Manual

Page 30

3–10

Chapter 3: Parameter Settings

Optional Features

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

f

For more information, refer to

“Status Processor” on page 4–7

.

FIFO RAM Blocks

The option to select 2 FIFO RAM blocks depends on the parameters you select on the

Basic Parameters tab. These parameters affect the FIFO buffer size and FIFO buffer

width, both of which play a role in memory utilization.

When you select 2 FIFO RAM blocks, the timing performance of the IP core may

decrease (because the memory rdata bus is unregistered, as opposed to registered for

4 FIFO RAM blocks

). Altera recommends that you do full compilations for both

configurations before deciding which one to choose.

1

Use 2 FIFO RAM block only if it gives an improvement in memory utilization and if

your timing requirements are still met.

Table 3–3

shows the support for the 2 FIFO RAM block. 4 FIFO RAM block supports

all configuration.

Hungry

Starving or Hungry

Hungry

Hungry

Satisfied

Satisfied

Satisfied

Any

Satisfied

Table 3–3. User-Controlled Option (Part 2 of 2)

User Status Value

FIFO Buffer Status Value

Sent Status Value

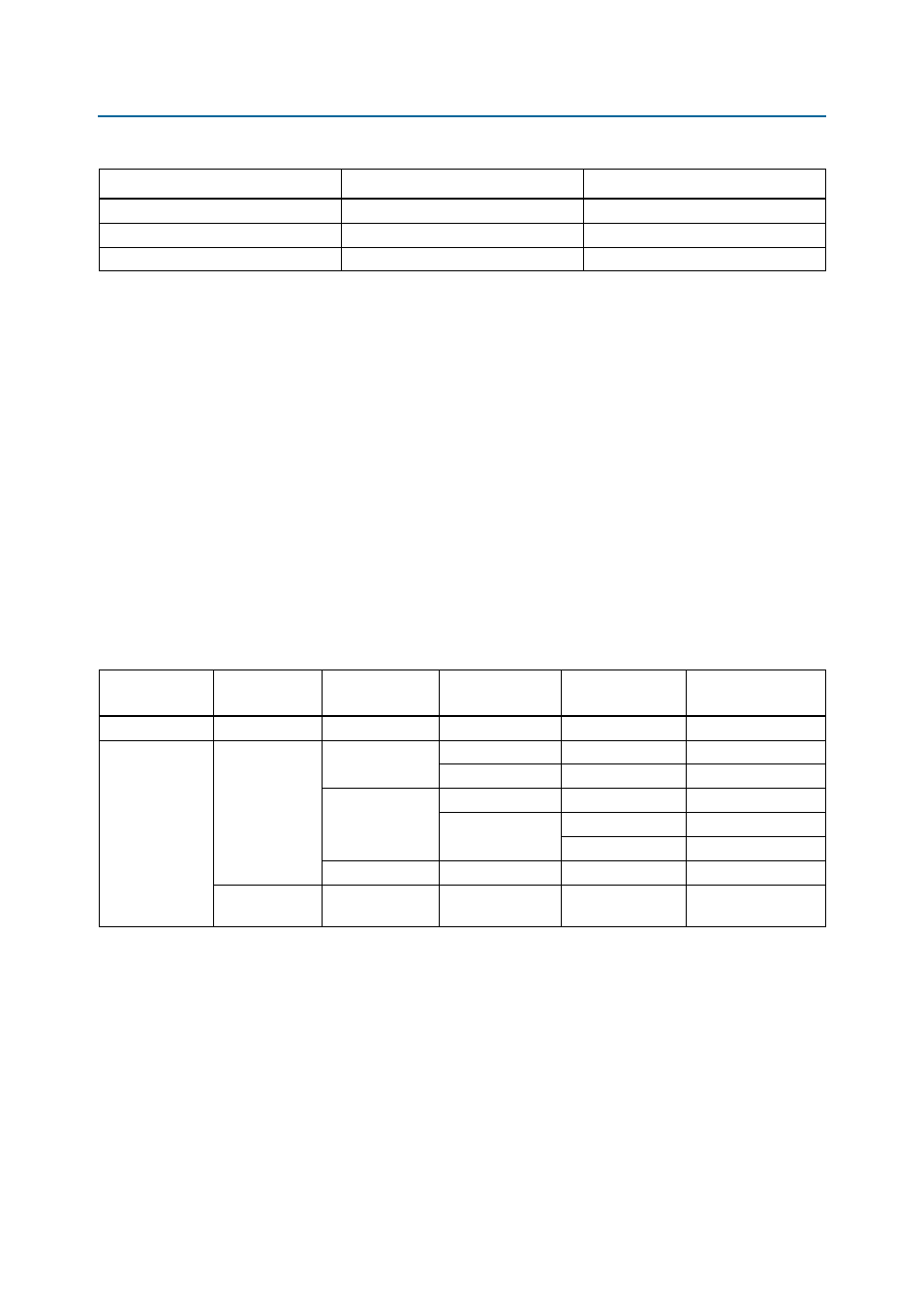

Table 3–4. 2 RAM Block Support

Data Flow

Direction

Buffer Mode

Data Path Width

Atlantic Interface

Width

Lite Transmitter

2 RAM Block Support

Receiver

Any

Any

Any

—

Yes

Transmitter

Shared Buffer

with Embedded

Addressing

32

32

—

No

64

—

Yes

64

64

Any

No

128

Yes

Yes

No

No

128

128

Any

No

Individual

Buffers

Any

Any

Any

Yes