Simulate the design, Use the testbench with the modelsim simulator – Altera POS-PHY Level 4 IP Core User Manual

Page 17

Chapter 2: Getting Started

2–7

Simulate the Design

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

1. After you review the generation report, click Exit to close the parameter editor.

The custom IP core variation is integrated into your design. You are now ready to

simulate and compile.

Simulate the Design

You can simulate your design using the VHDL and Verilog HDL IP functional

simulation models.

f

For more information on IP functional simulation models, including NativeLink, refer

to

“Simulate the Design” on page 2–7

and the

chapter in volume 3 of the Quartus II Handbook.

Altera provides models you can use for functional verification of the POS-PHY Level

4 IP core within your design. A Verilog HDL testbench, including scripts to run it, is

also provided. This testbench, for use with the ModelSim-Altera simulator or other

simulator tools via NativeLink, demonstrates how to instantiate a model in a design.

This section tells you how to use the testbench with the ModelSim simulator or with

other simulators via NativeLink.

f

For a list of the simulators that you can use with NativeLink, refer to the

hapter in volume 3 of the Quartus II Handbook.

c

The testbench is in Verilog HDL, so you require a license to run mixed language

simulations to run the testbench with the VHDL model. If you edit any of your

variation’s clear-text Verilog HDL files, you must update the IP functional simulation

model before running the simulator. To update the model, run the quartus_sh -t

Use the Testbench with the ModelSim Simulator

To use the testbench with IP functional simulation models in the ModelSim simulator,

follow these steps:

1. Start the ModelSim simulator.

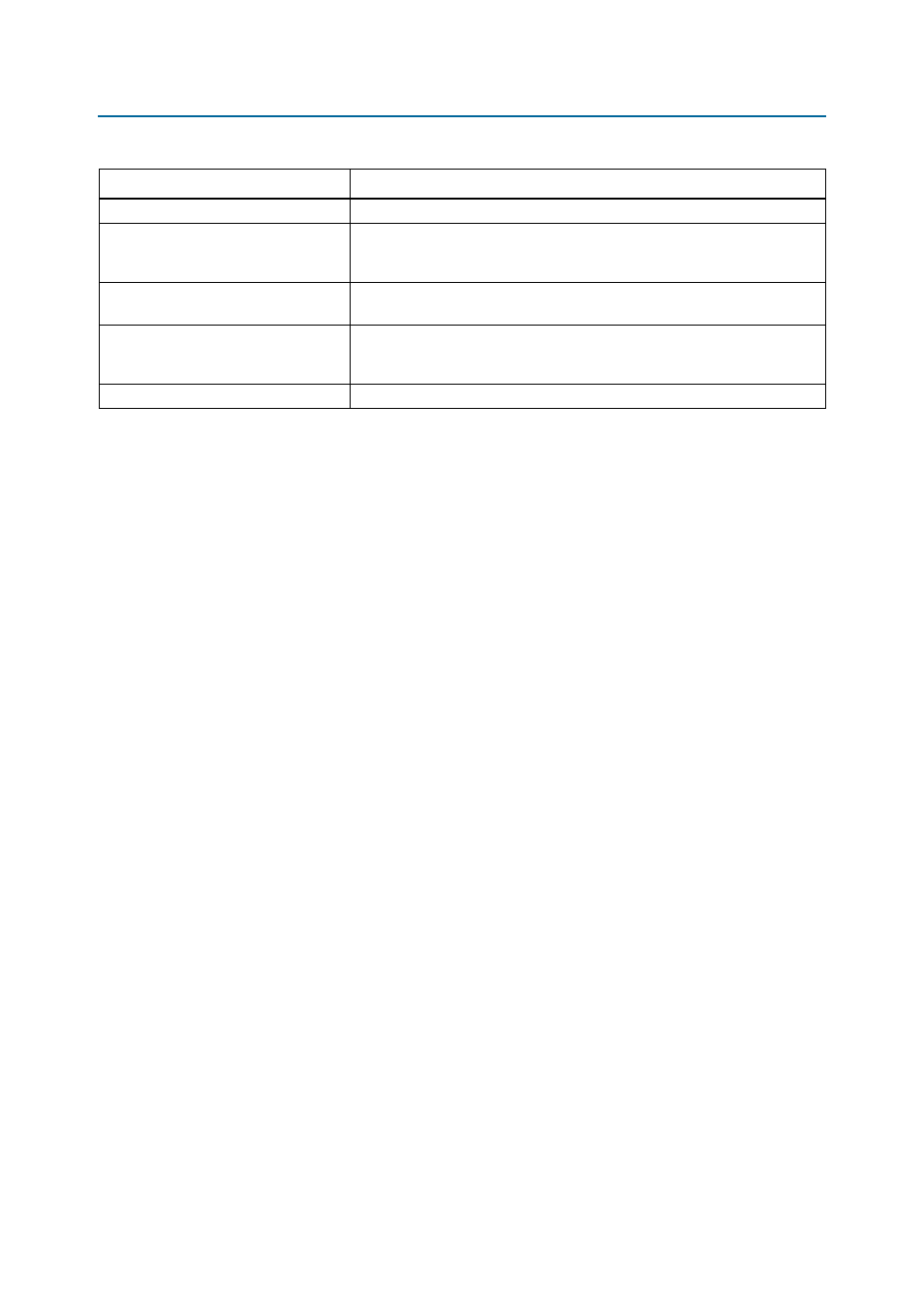

<variation name>.html

The IP core report file.

<variation name>.ppf

XML file that describes the IP core pin attributes to the Quartus II Pin Planner. IP

core pin attributes include pin direction, location, I/O standard assignments, and

drive strength.

<variation name>.sdc

TimeQuest SDC constraint settings file for timing analysis. Use this file to

specify constraints required for TimeQuest analysis.

<variation name>.v or .vhd

A IP core variation file, which defines a Verilog HDL top-level description of the

custom IP core. Instantiate the entity defined by this file inside of your design.

Include this file when compiling your design in the Quartus II software.

<variation_name>.vo or .vho

Verilog HDL IP functional simulation model.

Table 2–1. Generated Files (Part 2 of 2)

File

Description