Table 1–4, Table 1–5 – Altera POS-PHY Level 4 IP Core User Manual

Page 8

1–6

Chapter 1: About This IP Core

Performance and Resource Utilization

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

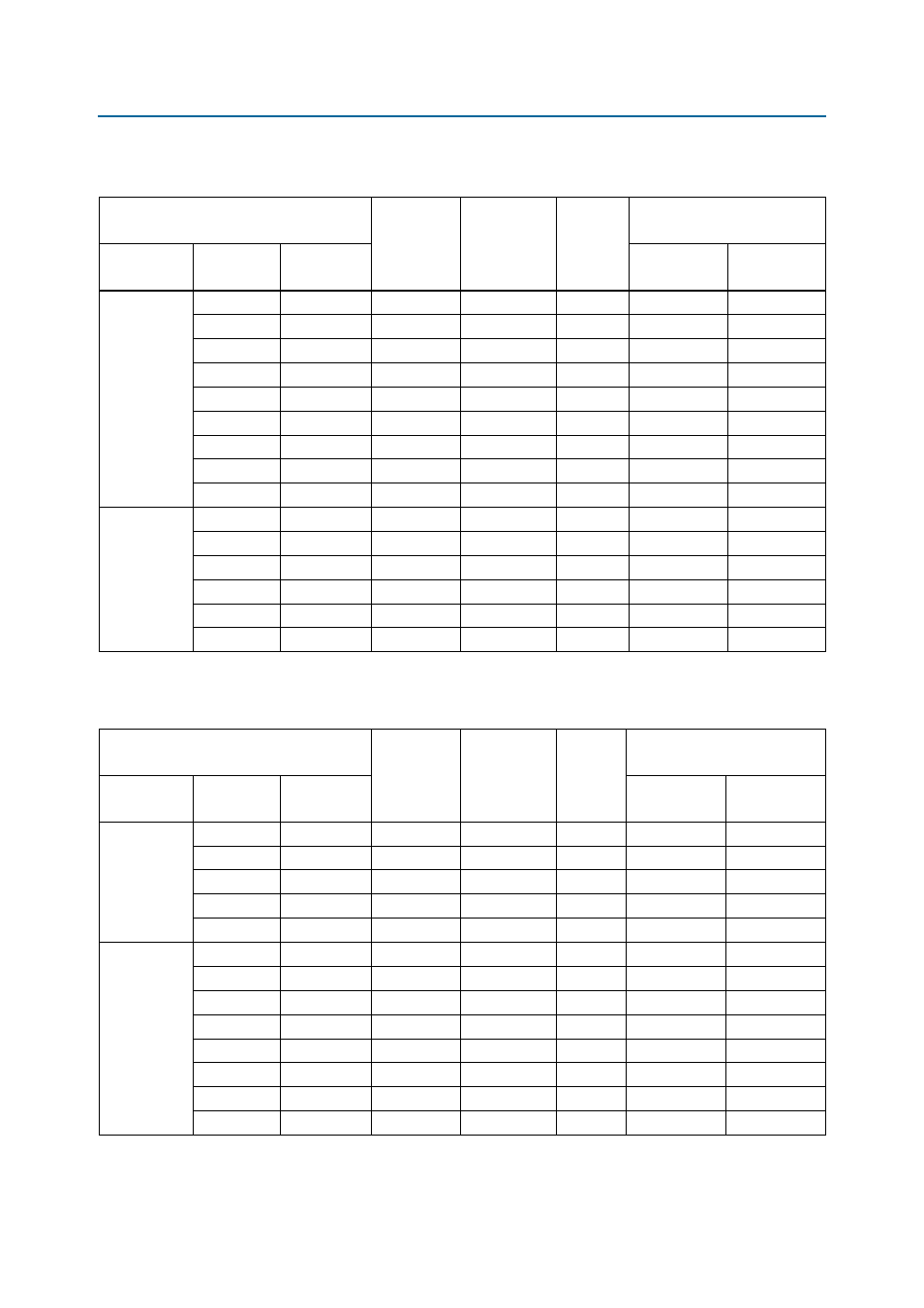

Table 1–4. Performance—Shared Buffer With Embedded Addressing Mode—Stratix IV Devices

Parameters

ALUTs

Logic

Registers

Memory

Blocks

(M9K)

clk

f

MAX

(MHz)

Data Flow

Direction

Data Path

Width (bits)

Number of

Ports

EP4SGX70

DF29C3

EP4SGX230

DF29C3ES

Receiver

32

1

1,190

1,294

6

204

195

64

1

1,387

1,820

16

261

284

128

1

2,215

2,741

30

186

207

32

4

1,198

1,300

6

199

156

64

4

1,398

1,826

16

273

273

128

4

2,221

2,742

30

195

195

32

10

1,138

1,249

7

213

163

64

10

1,396

1,782

18

281

270

128

10

2,273

2,709

33

187

160

Transmitter

32

4

1,049

1,085

5

192

185

64

4

1,032

1,454

9

262

232

128

4

1,178

1,464

17

175

181

32

10

1,023

1,119

5

178

163

64

10

1,057

1,601

9

260

225

128

10

1,331

1,770

17

190

166

Table 1–5. Performance—Individual Buffers Mode—Stratix IV Devices

Parameters

ALUTs

Logic

Registers

Memory

Blocks

(M9K)

clk

f

MAX

(MHz)

Data Flow

Direction

Data Path

Width (bits)

Number of

Ports

EP4SGX70

DF29C3

EP4SGX230

DF29C3ES

Receiver

32

4

2,245

2,427

21

182

159

64

4

2,514

2,800

40

270

268

128

4

3,833

4,160

78

165

149

32

10

4,070

4,529

45

140

144

64

10

4,823

4,830

88

255

254

Transmitter

32

1

1,155

1,213

6

165

176

64

1

1,309

1,784

10

245

182

128

1

1,710

2,245

18

177

171

32

4

2,563

2,524

18

130

151

64

4

2,726

2,997

34

183

212

128

4

3,430

3,778

66

166

153

32

10

5,210

4,789

42

120

118

64

10

5,733

5,188

82

153

213