Altera POS-PHY Level 4 IP Core User Manual

Page 132

G–2

Appendix G: Conversion from v2.2.x

Receiver Signals

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

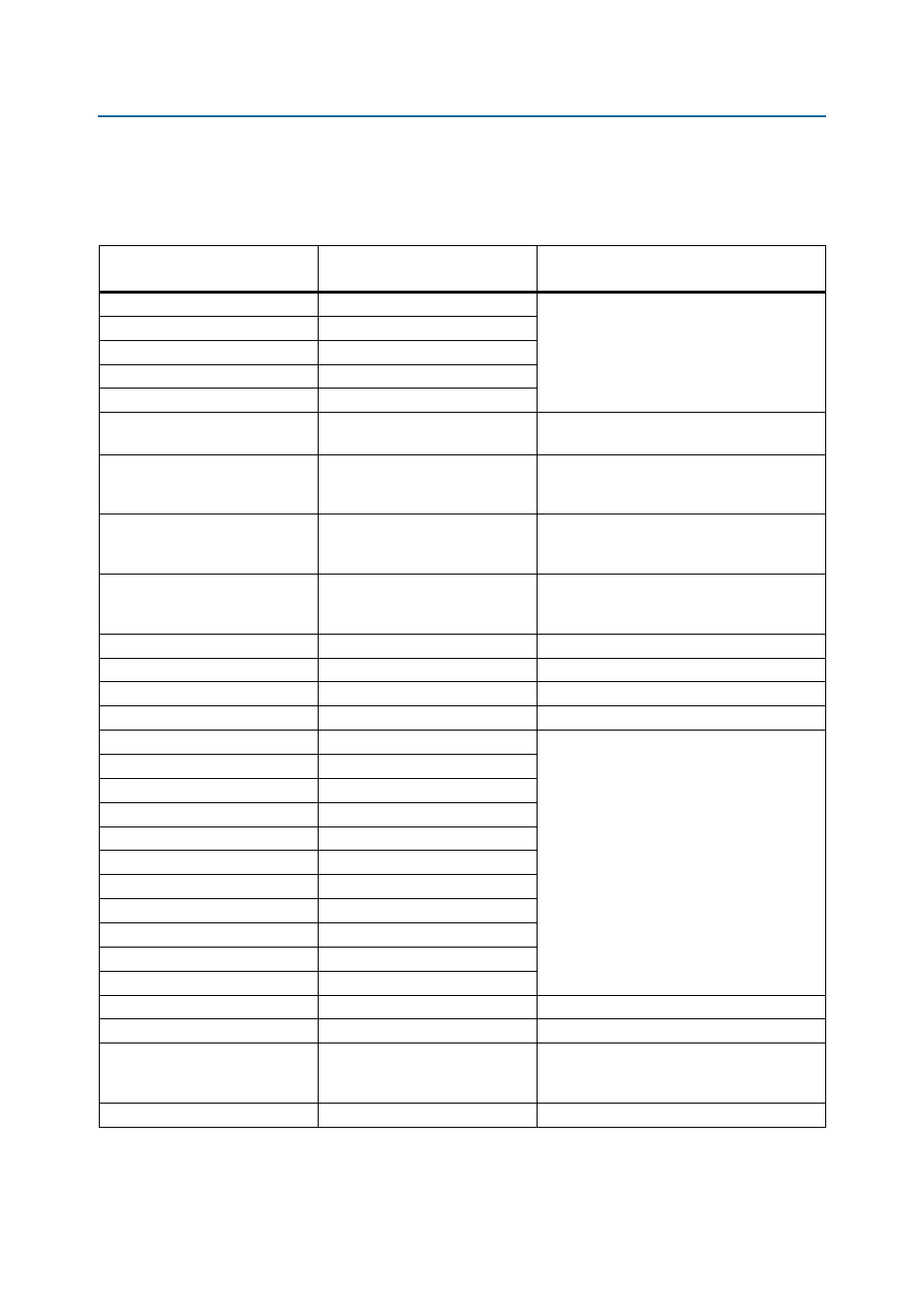

Table G–1

shows the new v2.4.x and 2.3.x receiver signal names as they exist in the

top-level file, their equivalent v2.2.x signal names (if applicable), and notes explaining

the changes.

Table G–1. Receiver Signal Changes (Part 1 of 3)

Version 2.4.x and 2.3.x Signal

Name

Version 2.2.x Signal Name

Notes

rdclk

rdclk

No change.

rctl

rctl

rdat[15:0]

rdat[15:0]

rsclk

rsclk

rstat[1:0]

rstat[1:0]

rdint_clk

rrefclk

Clock derived from rdclk. Signals infixed by

_rd_

are synchronous to this domain.

rdint_reset_n

–

New. Tied high in the IP Toolbench top-level file.

Refer to

usage.

rxsys_clk

a0_arxclk

System clock. Signals infixed by _ry_ are

synchronous to this clock. Refer to

for usage.

rxsys_reset_n

–

New. Tied high in the IP Toolbench top-level file.

Refer to

usage.

rxreset_n

rxreset_n

No change. Resets all domains.

rxinfo_aot[12:0]

rxinfo_aot[15:0]

Change in port width.

aN_arxclk

aN_arxclk

No change.

aN_arxreset_n

aN_arxreset_n

Tied high in the IP Toolbench top-level file.

aN_arxdav

aN_arxdav

No change.

aN_arxena

aN_arxena

aN_arxdat

aN_arxdat

aN_arxval

aN_arxval

aN_arxsop

aN_arxsop

aN_arxeop

aN_arxeop

aN_arxmty

aN_arxmty

aN_arxerr

aN_arxerr

aN_arxadr

aN_arxadr

ctl_ax_ftl

ctl_a0_rxftl

ctl_ax_fifo_eopdav

ctl_xx_fifo_eopdav

err_aN_fifo_parityN

–

New.

stat_aN_fifo_emptyN

stat_a0_rxfifo_empty

No change.

err_ry_fifo_oflwN

err_xx_rxfifo_oflw

In version 2.2.x, this signal is in the rrefclk

domain; in version 2.3.0, this signal is in the

rxsys_clk

domain.

ctl_ry_errchk_chkpkt

ctl_xx_errchk_chpkt

No change.