Signals – Altera POS-PHY Level 4 IP Core User Manual

Page 61

Chapter 4: Functional Description—Receiver

4–23

Signals

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

Signals

Table 4–5

through

Table 4–11

list the I/O signals used in the receiver IP core. The

active low signals are suffixed by _n.

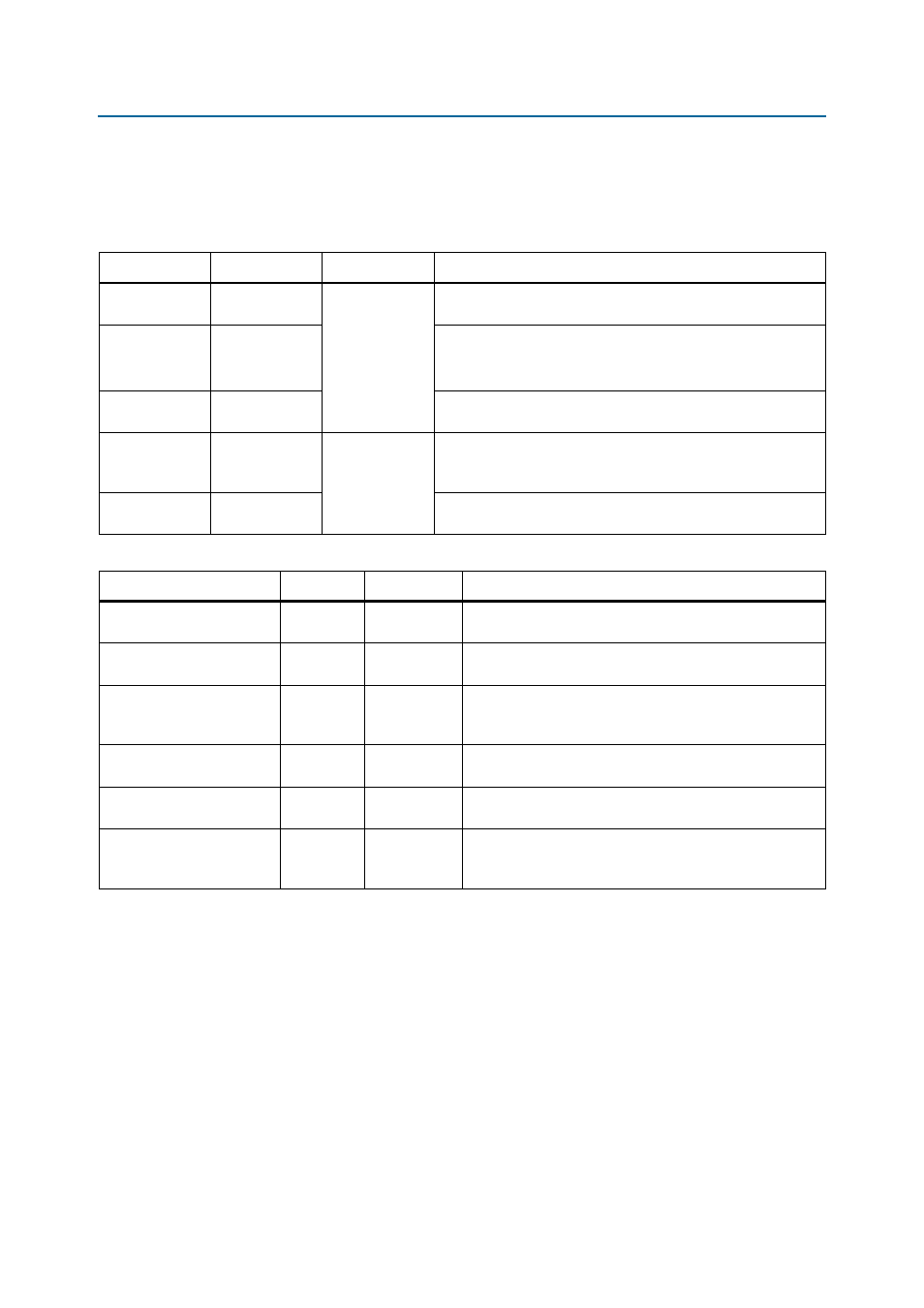

Table 4–5. SPI-4.2 Receive Interface

Signal

Direction

Clock Domain

Description

rdclk

LVDS Clock

Input

rdclk

SPI-4.2 differential receive clock. Double-data rate clock

synchronous to rctl and rdat.

rctl

LVDS Input

SPI-4.2 differential receive control.

When set to a logic 1, the word on rdat is a control word. When

set to a logic 0, the word on rdat is a payload word.

rdat[15:0]

LVDS Input

SPI-4.2 differential receive data bus. Bus carries packets/cells or

in-band control words.

rsclk

LVTTL Output

rsclk

(rdint_clk)

SPI-4.2 receive status clock. This signal uses a regular LVTTL

data pin instead of a dedicated output clock pin. Derived from

rdclk

. Active if rdclk is active.

rstat[1:0]

LVTTL Output

SPI-4.2 receive status channel. Indicates the downstream

device’s FIFO buffers’ fill level to the upstream device’s scheduler.

Table 4–6. Global

Signal

Direction

Clock Domain

Description

rdint_clk

Output

rdint_clk

Derived from rdclk. Signals infixed with _rd_ are

synchronous to this clock. Active if rdclk is active.

rxsys_clk

Input

rxsys_clk

System clock. Signals infixed with _ry_ are synchronous to

this clock.

rxreset_n

Input

Asynchronous

Active low asynchronous reset to all internal logic, including

Atlantic FIFO buffers. Refer to

rxinfo_aot[12:0]

Output

Static

Fixed output information signal that contains the current

AOT number for the release.

stat_rx_pll_locked

Output

Asynchronous

Locked signal directly from fast PLL in ALTVDS for full rate

variations, or enhanced PLL in quarter-rate variations.

ctl_rx_pll_areset

Input

Asynchronous

Asynchronous reset signal directly to fast PLL in ALTVDS for

full rate variations, or enhanced PLL in quarter-rate

variations.